Một số giải pháp thiết kế, mô phỏng đặc tuyến của bộ khuếch đại công suất cao tần dải rộng 25W

Nghiên cứu các bộ khuếch đại tần số cao, đặc biệt là dải sóng cực

ngắn sử dụng công nghệ mạch rắn tích hợp đã được tập trung nghiên cứu và phát

triển mạnh trong những năm gần đây. Bài báo này trình bày một phương án thiết kế

và đặc tính hóa của bộ khuếch đại mạch rắn tích hợp công suất 25W dải rộng. Việc

lựa chọn kiến trúc và trình tự thiết kế mạch dựa trên các mô phỏng ADS cho các

khối được xây dựng như các modul: khuếch đại, ổn định, mạng phối hợp đầu vào và

đầu ra. Các đại lượng đặc trưng chính như công suất đầu ra, biến đổi của hệ số

tăng ích, hiệu quả PAE, đối với hoạt động của bộ khuếch đại được mô tả trong thời

gian thực. Đặc tính hóa ở mức độ linh kiện cũng như mức độ hệ thống của bộ

khuếch đại này là dữ liệu hữu ích cho các nhà thiết kế RF làm việc trong lĩnh vực

truyền thông, công nghiệp, y tế, quốc phòng,

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Tóm tắt nội dung tài liệu: Một số giải pháp thiết kế, mô phỏng đặc tuyến của bộ khuếch đại công suất cao tần dải rộng 25W

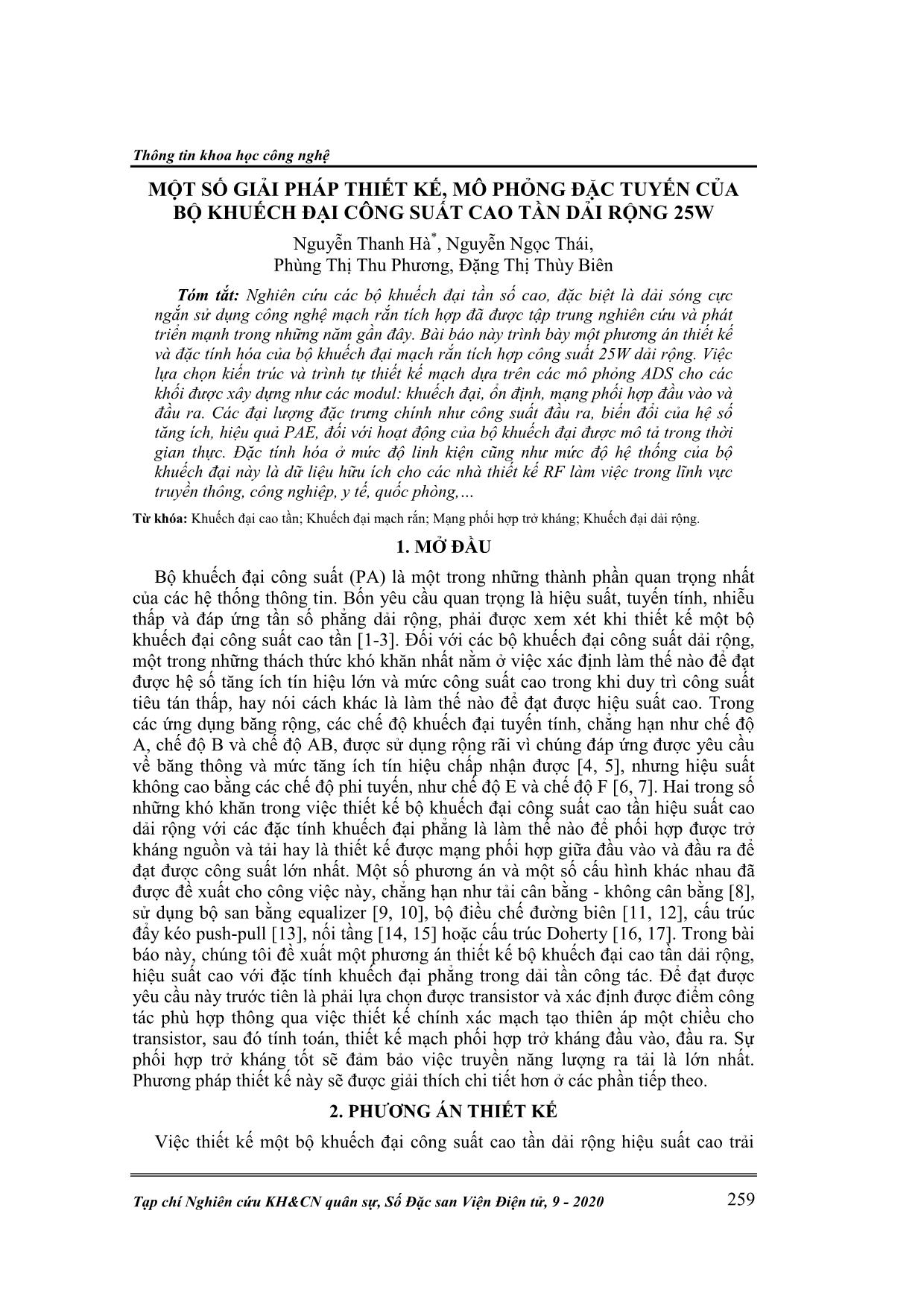

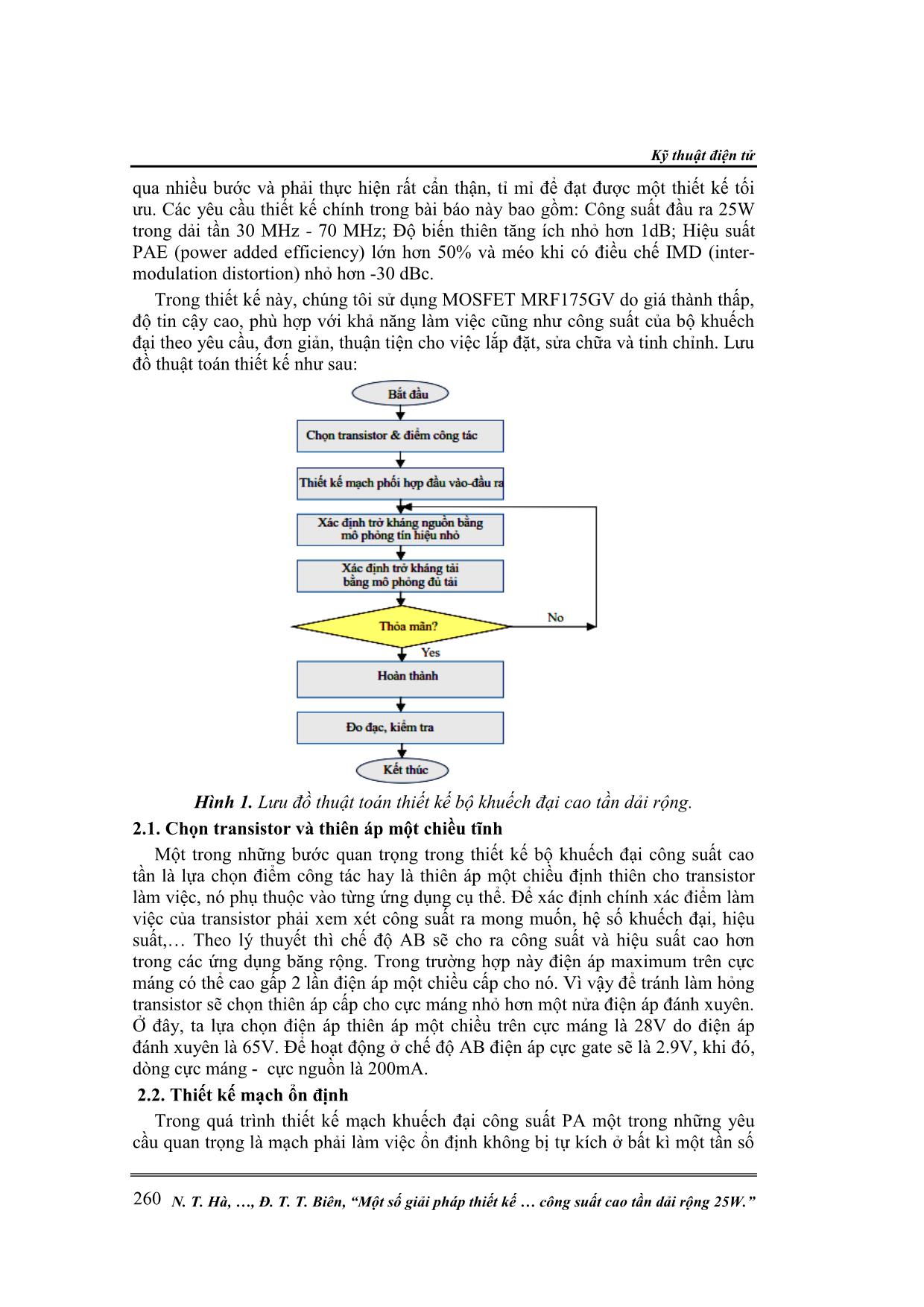

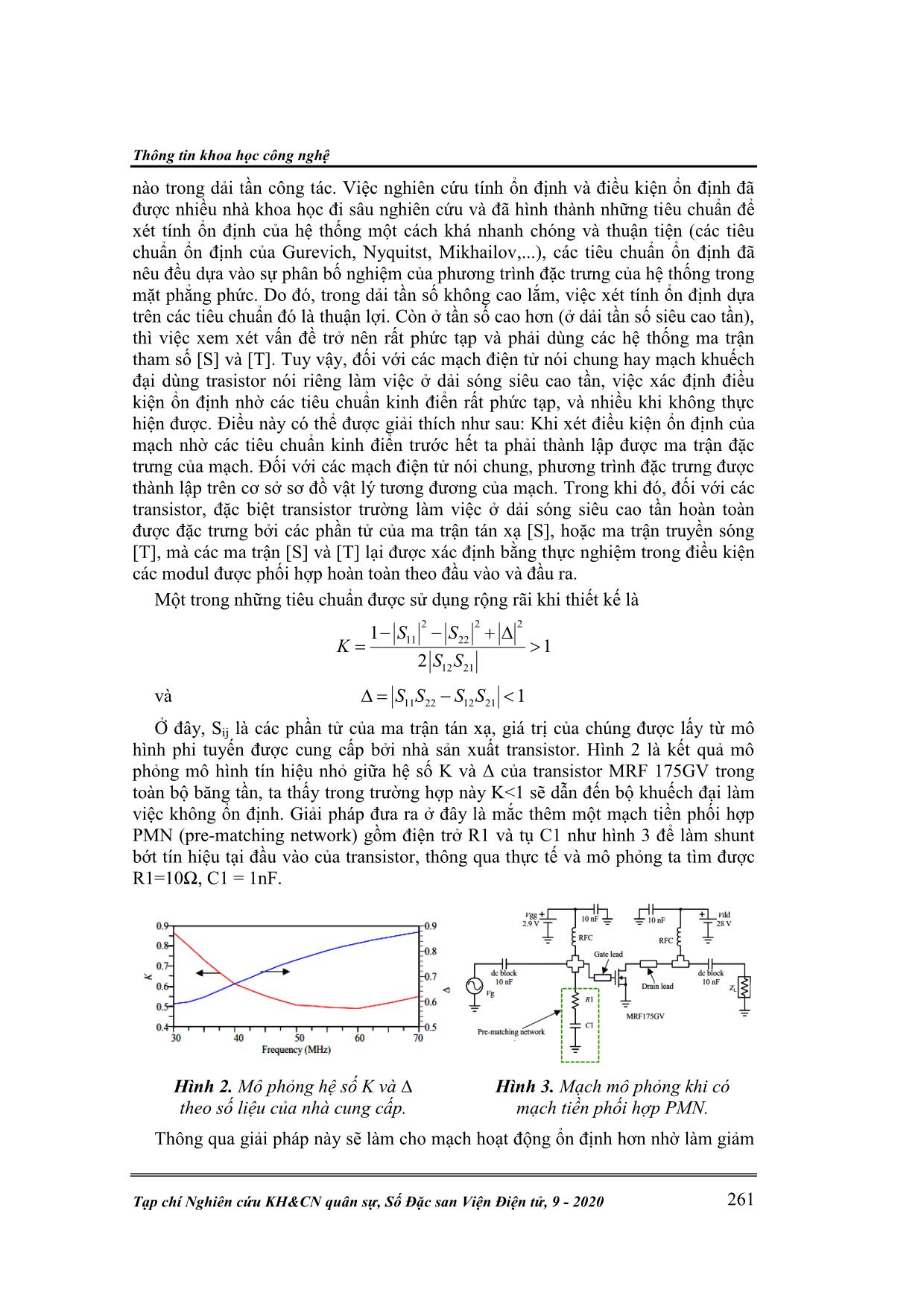

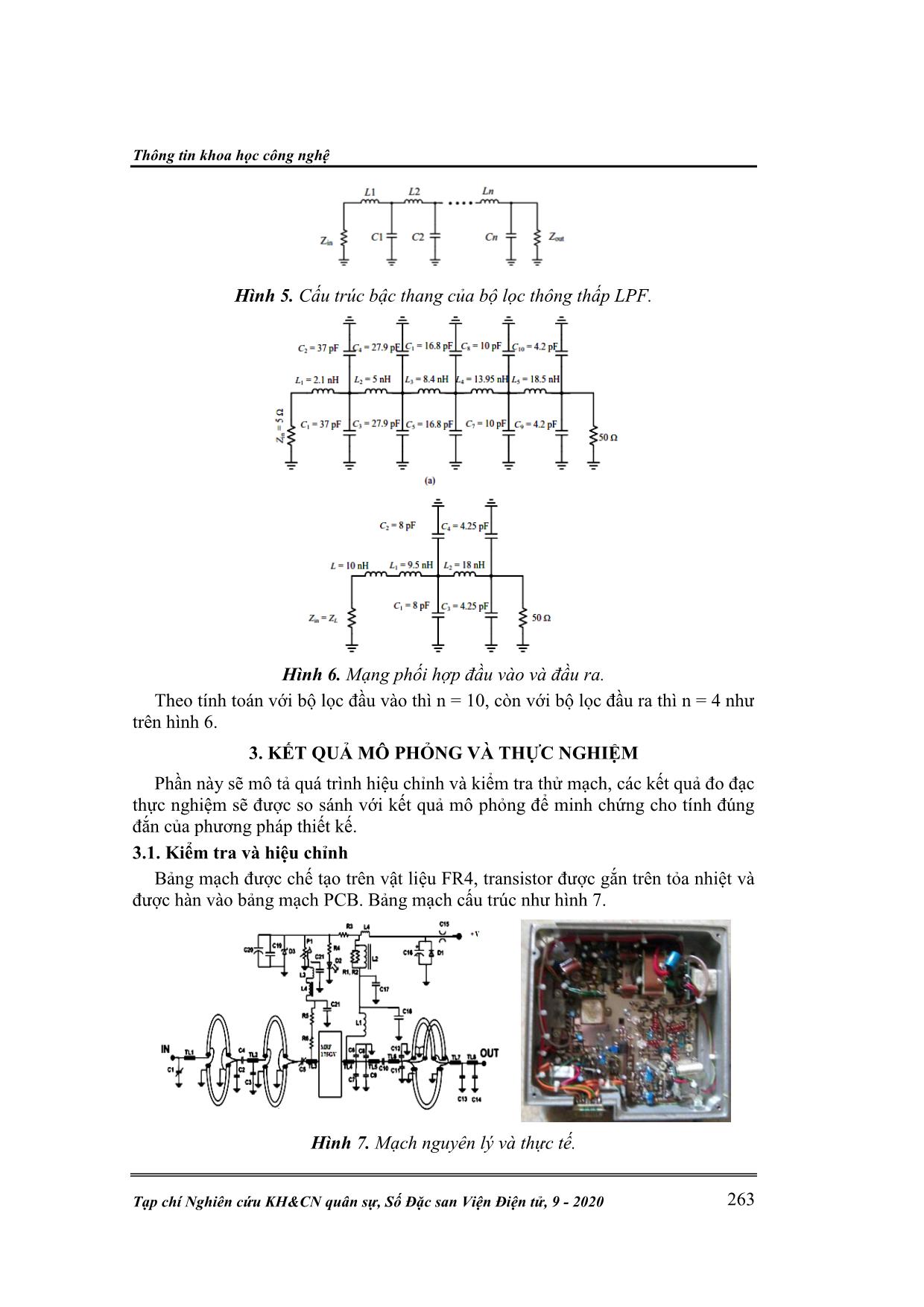

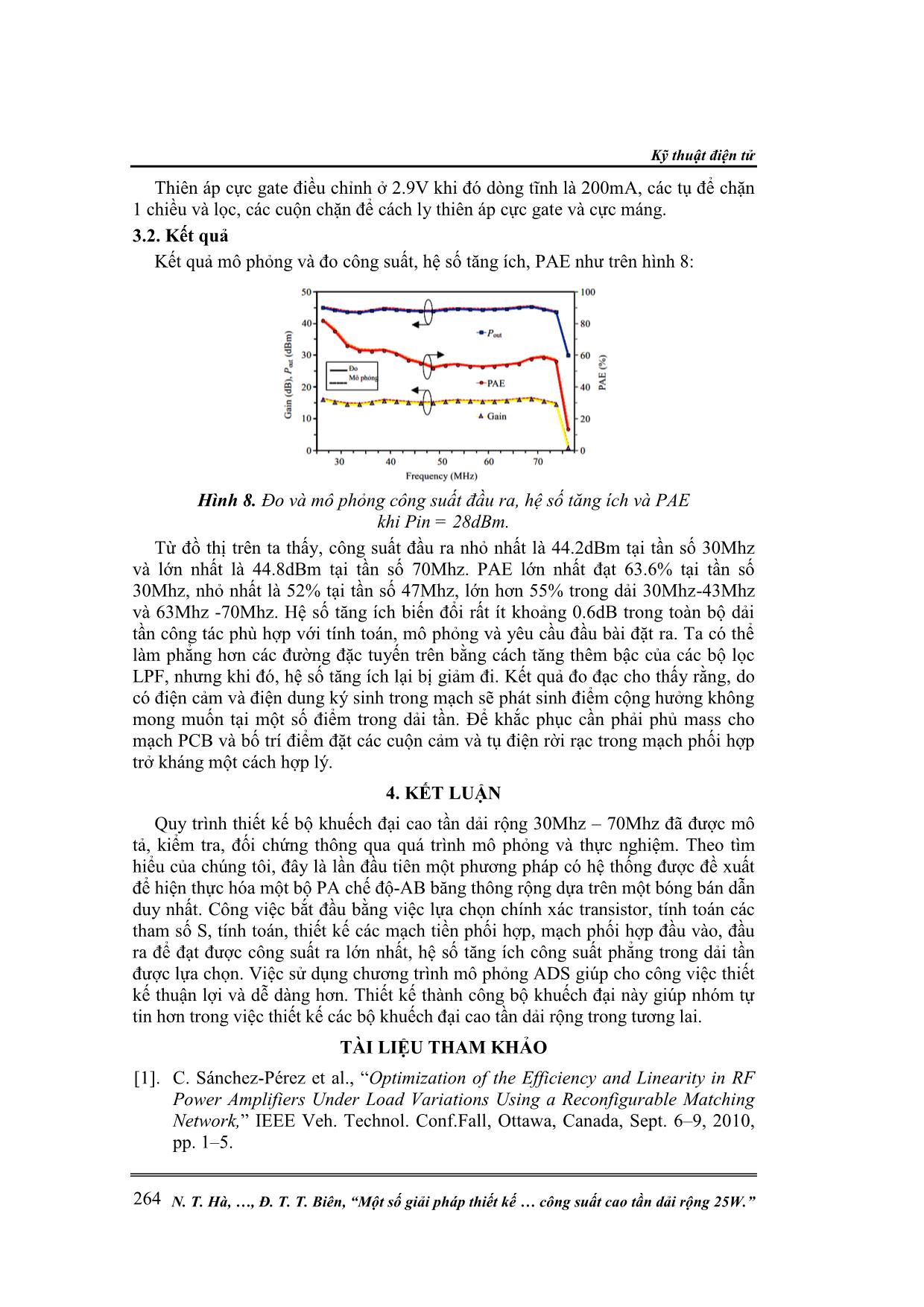

Thông tin khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số Đặc san Viện Điện tử, 9 - 2020 259 MỘT SỐ GIẢI PHÁP THIẾT KẾ, MÔ PHỎNG ĐẶC TUYẾN CỦA BỘ KHUẾCH ĐẠI CÔNG SUẤT CAO TẦN DẢI RỘNG 25W Nguyễn Thanh Hà*, Nguyễn Ngọc Thái, Phùng Thị Thu Phương, Đặng Thị Thùy Biên Tóm tắt: Nghiên cứu các bộ khuếch đại tần số cao, đặc biệt là dải sóng cực ngắn sử dụng công nghệ mạch rắn tích hợp đã được tập trung nghiên cứu và phát triển mạnh trong những năm gần đây. Bài báo này trình bày một phương án thiết kế và đặc tính hóa của bộ khuếch đại mạch rắn tích hợp công suất 25W dải rộng. Việc lựa chọn kiến trúc và trình tự thiết kế mạch dựa trên các mô phỏng ADS cho các khối được xây dựng như các modul: khuếch đại, ổn định, mạng phối hợp đầu vào và đầu ra. Các đại lượng đặc trưng chính như công suất đầu ra, biến đổi của hệ số tăng ích, hiệu quả PAE, đối với hoạt động của bộ khuếch đại được mô tả trong thời gian thực. Đặc tính hóa ở mức độ linh kiện cũng như mức độ hệ thống của bộ khuếch đại này là dữ liệu hữu ích cho các nhà thiết kế RF làm việc trong lĩnh vực truyền thông, công nghiệp, y tế, quốc phòng, Từ khóa: Khuếch đại cao tần; Khuếch đại mạch rắn; Mạng phối hợp trở kháng; Khuếch đại dải rộng. 1. MỞ ĐẦU Bộ khuếch đại công suất (PA) là một trong những thành phần quan trọng nhất của các hệ thống thông tin. Bốn yêu cầu quan trọng là hiệu suất, tuyến tính, nhiễu thấp và đáp ứng tần số phẳng dải rộng, phải được xem xét khi thiết kế một bộ khuếch đại công suất cao tần [1-3]. Đối với các bộ khuếch đại công suất dải rộng, một trong những thách thức khó khăn nhất nằm ở việc xác định làm thế nào để đạt được hệ số tăng ích tín hiệu lớn và mức công suất cao trong khi duy trì công suất tiêu tán thấp, hay nói cách khác là làm thế nào để đạt được hiệu suất cao. Trong các ứng dụng băng rộng, các chế độ khuếch đại tuyến tính, chẳng hạn như chế độ A, chế độ B và chế độ AB, được sử dụng rộng rãi vì chúng đáp ứng được yêu cầu về băng thông và mức tăng ích tín hiệu chấp nhận được [4, 5], nhưng hiệu suất không cao bằng các chế độ phi tuyến, như chế độ E và chế độ F [6, 7]. Hai trong số những khó khăn trong việc thiết kế bộ khuếch đại công suất cao tần hiệu suất cao dải rộng với các đặc tính khuếch đại phẳng là làm thế nào để phối hợp được trở kháng nguồn và tải hay là thiết kế được mạng phối hợp giữa đầu vào và đầu ra để đạt được công suất lớn nhất. Một số phương án và một số cấu hình khác nhau đã được đề xuất cho công việc này, chẳng hạn như tải cân bằng - không cân bằng [8], sử dụng bộ san bằng equalizer [9, 10], bộ điều chế đường biên [11, 12], cấu trúc đẩy kéo push-pull [13], nối tầng [14, 15] hoặc cấu trúc Doherty [16, 17]. Trong bài báo này, chúng tôi đề xuất một phương án thiết kế bộ khuếch đại cao tần dải rộng, hiệu suất cao với đặc tính khuếch đại phẳng trong dải tần công tác. Để đạt được yêu cầu này trước tiên là phải lựa chọn được transistor và xác định được điểm công tác phù hợp thông qua việc thiết kế chính xác mạch tạo thiên áp một chiều cho transistor, sau đó tính toán, thiết kế mạch phối hợp trở kháng đầu vào, đầu ra. Sự phối hợp trở kháng tốt sẽ đảm bảo việc truyền năng lượng ra tải là lớn nhất. Phương pháp thiết kế này sẽ được giải thích chi tiết hơn ở các phần tiếp theo. 2. PHƯƠNG ÁN THIẾT KẾ Việc thiết kế một bộ khuếch đại công suất cao tần dải rộng hiệu suất cao trải Kỹ thuật điện tử N. T. Hà, , Đ. T. T. Biên, “Một số giải pháp thiết kế công suất cao tần dải rộng 25W.” 260 qua nhiều bước và phải thực hiện rất cẩn thận, tỉ mỉ để đạt được một thiết kế tối ưu. Các yêu cầu thiết kế chính trong bài báo này bao gồm: Công suất đầu ra 25W trong dải tần 30 MHz - 70 MHz; Độ biến thiên tăng ích nhỏ hơn 1dB; Hiệu suất PAE (power added efficiency) lớn hơn 50% và méo khi có điều chế IMD (inter- modulation distortion) nhỏ hơn -30 dBc. Trong thiết kế này, chúng tôi sử dụng MOSFET MRF175GV do giá thành thấp, độ tin cậy cao, phù hợp với khả năng làm việc cũng như công suất của bộ khuếch đại theo yêu cầu, đơn giản, thuận tiện cho việc lắp đặt, sửa chữa và tinh chỉnh. Lưu đồ thuật toán thiết kế như sau: Hình 1. Lưu đồ thuật toán thiết kế bộ khuếch đại cao tần dải rộng. 2.1. Chọn transistor và thiên áp một chiều tĩnh Một trong những bước quan trọng trong thiết kế bộ khuếch đại công suất cao tần là lựa chọn điểm công tác hay là thiên áp một chiều định thiên cho transistor làm việc, nó phụ thuộc vào từng ứng dụng cụ thể. Để xác định chính xác điểm làm việc của transistor phải xem xét công suất ra mong muốn, hệ số khuếch đại, hiệu suất, Theo lý thuyết thì chế độ AB sẽ cho ra công suất và hiệu suất cao hơn trong các ứng dụng băng rộng. Trong trường hợp này điện áp maximum trên cực máng có thể cao gấp 2 lần điện áp một chiều cấp cho nó. Vì vậy để tránh làm hỏng transistor sẽ chọn thiên áp cấp cho cực máng nhỏ hơn một nửa điện áp đánh xuyên. Ở đây, ta lựa chọn điện áp thiên áp một chiều trên cực máng là 28V do điện áp đánh xuyên là 65V. Để hoạt động ở chế độ AB điện áp cực gate sẽ là 2.9V, khi đó, dòng cực máng - cực nguồn là 200mA. 2.2. Thiết kế mạch ổn định Trong quá trình thiết kế mạch khuếch đại công suất PA một trong những yêu cầu quan trọng là mạch phải làm việc ổn định không bị tự kích ở bất kì một tần số Thông tin khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số Đặc san Viện Điện tử, 9 - 2020 261 nào trong dải tần công tác. Việc nghiên cứu tính ổn định và điều kiện ổn định đã được nhiều nhà khoa học đi sâu nghiên cứu và đã hình thành những tiêu chuẩn để xét tính ổn định của hệ thống một cách khá nhanh chóng và thuận tiện (các tiêu chuẩn ổn định của Gurevich, Nyquitst, Mikhailov,...), các tiêu chuẩn ổn định đã nêu đều dựa vào sự phân bố nghiệm của phương trình đặc trưng của hệ thống trong mặt phẳng phức. Do đó, trong dải tần số không cao lắm, việc xét tính ổn định dựa trên các tiêu chuẩn đó là thuận lợi. Còn ở tần số cao hơn (ở dải tần số siêu cao tần), thì việc xem xét vấn đề trở nên rất phức tạp và phải dùng các hệ thống ma trận tham số [S] và [T]. Tuy vậy, đối với các mạch điện tử nói chung hay mạch khuếch đại dùng trasistor nói riêng làm việc ở dải sóng siêu cao tần, việc xác định điều kiện ổn định nhờ các tiêu chuẩn kinh điển rất phức tạp, và nhiều khi không thực hiện được. Điều này có thể được giải thích như sau: Khi xét điều kiện ổn định của mạch nhờ các tiêu chuẩn kinh điển trước hết ta phải thành lập được ma trận đặc trưng của mạch. Đối với các mạch điện tử nói chung, phương trình đặc trưng được thành lập trên cơ sở sơ đồ vật lý tương đương của mạch. Trong khi đó, đối với các transistor, đặc biệt transistor trường làm việc ở dải sóng siêu cao tần hoàn toàn được đặc trưng bởi các phần tử của ma trận tán xạ [S], hoặc ma trận truyền sóng [T], mà các ma trận [S] và [T] lại được xác định bằng thực nghiệm trong điều kiện các modul được phối hợp hoàn toàn theo đầu vào và đầu ra. Một trong những tiêu chuẩn được sử dụng rộng rãi khi thiết kế là 2 2 2 11 22 12 21 1 1 2 S S K S S và 11 22 12 21 1S S S S Ở đây, Sij là các phần tử của ma trận tán xạ, giá trị của chúng được lấy từ mô hình phi tuyến được cung cấp bởi nhà sản xuất transistor. Hình 2 là kết quả mô phỏng mô hình tín hiệu nhỏ giữa hệ số K và Δ của transistor MRF 175GV trong toàn bộ băng tần, ta thấy trong trường hợp này K<1 sẽ dẫn đến bộ khuếch đại làm việc không ổn định. Giải pháp đưa ra ở đây là mắc thêm một mạch tiền phối hợp PMN (pre-matching network) gồm điện trở R1 và tụ C1 như hình 3 để làm shunt bớt tín hiệu tại đầu vào của transistor, thông qua thực tế và mô phỏng ta tìm được R1=10Ω, C1 = 1nF. Hình 2. Mô phỏng hệ số K và ∆ theo số liệu của nhà cung cấp. Hình 3. Mạch mô phỏng khi có mạch tiền phối hợp PMN. Thông qua giải pháp này sẽ làm cho mạch hoạt động ổn định hơn nhờ làm giảm Kỹ thuật điện tử N. T. Hà, , Đ. T. T. Biên, “Một số giải pháp thiết kế công suất cao tần dải rộng 25W.” 262 sự biến đổi của hệ số tăng ích của mạch trong toàn bộ dải tần, đồng thời thay đổi một cách hiệu quả hệ số K và Δ thỏa mãn yêu cầu về tính ổn định như hình 4. Hình 4. Kết quả mô phỏng hệ số K và ∆ khi có mạch PMN. 2.3. Tính toán trở kháng nguồn và tải, thiết kế mạng phối hợp trở kháng đầu vào và đầu ra Khi thiết kế các mạch khuếch đại dùng transistor ở dải sóng siêu cao tần, chúng ta luôn mong muốn hệ số khuếch đại công suất của mạch thiết kế đạt giá trị lớn nhất. Điều đó có thể được thực hiện nhờ các mạch phối hợp ít tổn hao thiết lập trên đầu vào và đầu ra của transistor. Với mô hình tín hiệu nhỏ, hầu hết các bộ khuếch đại PA được coi như là tuyến tính, các ảnh hưởng phi tuyến được bỏ qua. Tuy nhiên, ở mô hình tín hiệu lớn, các ảnh hưởng của phi tuyến phải được xem xét đưa vào tính toán. Vì vậy, việc phân tích mạch hoạt động đủ nguồn/tải dựa trên mô phỏng hài và các phân tích phi tuyến là phương pháp tốt nhất để xác định chính xác trở kháng nguồn và trở kháng tải. Việc mô phỏng sử dụng một đường tròn trong giản đồ Smith như là một tham số chẳng hạn như PAE, công suất đầu ra, tăng ích tín hiệu, sẽ được xem xét với các trở kháng nguồn hoặc tải khác nhau. Có thể sử dụng tool EDA trong phần mềm ADS của Agilent để thực hiện mô phỏng này. Quá trình mô phỏng phải được thực hiện ít nhất 2 lần khi tính toán các trở kháng tối ưu do sự phụ thuộc của các kết quả vào các giá trị ban đầu của trở kháng nguồn và tải. Mạng phối hợp trở kháng đầu vào là mạng tích cực ít tổn hao sử dụng biến áp phối hợp là đường truyền vi dải (transmission line transformer) và khuếch đại theo mức. Nó được thiết kế để điều hưởng phần dung của trở kháng đầu vào biến áp là 12.5 Ω phối hợp với liên hợp phức của trở kháng vào của transistor. Mạng phối hợp trở kháng đầu ra thực hiện phối hợp liên hợp phức giữa trở kháng đầu ra của transistor và anten ra 50 Ω trong toàn bộ dải tần. Mạng phối hợp trở kháng đầu vào và đầu ra thực hiện maximum hệ số tăng ích công suất và minimum hệ số sóng đứng VSWR. Thông thường chúng là các mạch lọc thông thấp LPF kiểu Chebyshev, giá trị của các phần tử trong mạch LPF được tính toán theo công thức sau: ' k kR R r ; ' ' 1c k k c C C r ; ' ' c k k c L L r Ở đây: 'kR , ' kC , ' kL , k = 1, 2, và ' c (băng thông phân đoạn) là các phần tử của bộ lọc được chuẩn hóa; Rk, Ck, Lk, và ωc (tần số trung tâm) là các phần tử của bộ lọc được phân đoạn. Hình 5 mô tả cấu trúc liên kết bậc thang của bộ lọc thông thấp. Thông tin khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số Đặc san Viện Điện tử, 9 - 2020 263 Hình 5. Cấu trúc bậc thang của bộ lọc thông thấp LPF. Hình 6. Mạng phối hợp đầu vào và đầu ra. Theo tính toán với bộ lọc đầu vào thì n = 10, còn với bộ lọc đầu ra thì n = 4 như trên hình 6. 3. KẾT QUẢ MÔ PHỎNG VÀ THỰC NGHIỆM Phần này sẽ mô tả quá trình hiệu chỉnh và kiểm tra thử mạch, các kết quả đo đạc thực nghiệm sẽ được so sánh với kết quả mô phỏng để minh chứng cho tính đúng đắn của phương pháp thiết kế. 3.1. Kiểm tra và hiệu chỉnh Bảng mạch được chế tạo trên vật liệu FR4, transistor được gắn trên tỏa nhiệt và được hàn vào bảng mạch PCB. Bảng mạch cấu trúc như hình 7. Hình 7. Mạch nguyên lý và thực tế. Kỹ thuật điện tử N. T. Hà, , Đ. T. T. Biên, “Một số giải pháp thiết kế công suất cao tần dải rộng 25W.” 264 Thiên áp cực gate điều chỉnh ở 2.9V khi đó dòng tĩnh là 200mA, các tụ để chặn 1 chiều và lọc, các cuộn chặn để cách ly thiên áp cực gate và cực máng. 3.2. Kết quả Kết quả mô phỏng và đo công suất, hệ số tăng ích, PAE như trên hình 8: Hình 8. Đo và mô phỏng công suất đầu ra, hệ số tăng ích và PAE khi Pin = 28dBm. Từ đồ thị trên ta thấy, công suất đầu ra nhỏ nhất là 44.2dBm tại tần số 30Mhz và lớn nhất là 44.8dBm tại tần số 70Mhz. PAE lớn nhất đạt 63.6% tại tần số 30Mhz, nhỏ nhất là 52% tại tần số 47Mhz, lớn hơn 55% trong dải 30Mhz-43Mhz và 63Mhz -70Mhz. Hệ số tăng ích biến đổi rất ít khoảng 0.6dB trong toàn bộ dải tần công tác phù hợp với tính toán, mô phỏng và yêu cầu đầu bài đặt ra. Ta có thể làm phẳng hơn các đường đặc tuyến trên bằng cách tăng thêm bậc của các bộ lọc LPF, nhưng khi đó, hệ số tăng ích lại bị giảm đi. Kết quả đo đạc cho thấy rằng, do có điện cảm và điện dung ký sinh trong mạch sẽ phát sinh điểm cộng hưởng không mong muốn tại một số điểm trong dải tần. Để khắc phục cần phải phủ mass cho mạch PCB và bố trí điểm đặt các cuộn cảm và tụ điện rời rạc trong mạch phối hợp trở kháng một cách hợp lý. 4. KẾT LUẬN Quy trình thiết kế bộ khuếch đại cao tần dải rộng 30Mhz – 70Mhz đã được mô tả, kiểm tra, đối chứng thông qua quá trình mô phỏng và thực nghiệm. Theo tìm hiểu của chúng tôi, đây là lần đầu tiên một phương pháp có hệ thống được đề xuất để hiện thực hóa một bộ PA chế độ-AB băng thông rộng dựa trên một bóng bán dẫn duy nhất. Công việc bắt đầu bằng việc lựa chọn chính xác transistor, tính toán các tham số S, tính toán, thiết kế các mạch tiền phối hợp, mạch phối hợp đầu vào, đầu ra để đạt được công suất ra lớn nhất, hệ số tăng ích công suất phẳng trong dải tần được lựa chọn. Việc sử dụng chương trình mô phỏng ADS giúp cho công việc thiết kế thuận lợi và dễ dàng hơn. Thiết kế thành công bộ khuếch đại này giúp nhóm tự tin hơn trong việc thiết kế các bộ khuếch đại cao tần dải rộng trong tương lai. TÀI LIỆU THAM KHẢO [1]. C. Sánchez-Pérez et al., “Optimization of the Efficiency and Linearity in RF Power Amplifiers Under Load Variations Using a Reconfigurable Matching Network,” IEEE Veh. Technol. Conf.Fall, Ottawa, Canada, Sept. 6–9, 2010, pp. 1–5. Thông tin khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số Đặc san Viện Điện tử, 9 - 2020 265 [2]. P. Medrel et al., “Time Domain Envelope Characterization of Power Amplifiers for Linear and High Efficiency Design Solutions,” IEEE Annu.Wireless Microw. Technol. Conf., Orlando, FL, USA, Apr. 7–9, 2013, pp. 1–6. [3]. W. Ga et al., “A Highly Linear Low Noise Amplifier with Wide Range Derivative Superposition Method,” IEEE Microw.Wireless Compon. Lett., vol. 25, no. 12, Dec. 2015, pp. 817–819. [4]. J.J. Yan et al., “Design of a 4-W Envelope Tracking Power Amplifier with More Than One Octave Carrier Bandwidth,” IEEE J. Solid-State Circuits, vol. 47, no. 10, Oct. 2012, pp. 2298–2308. [5]. J.J. Ya et al., “Broadband High PAE GaN Push-Pull Power Amplifier for 500 MHz to 2.5 GHz Operation,” IEEE MTT-S Int.Microw. Symp. Dig., Seattle, WA, USA, June 2–7, 2013, pp. 1–3. [6]. N. Tuffy, A. Zhu, and T.J. Brazil, “Novel Realisation of a Broadband High- Efficiency Continuous Class-F Power Amplifier,” European Microw. Integr. Circuits Conf., Manchester, UK, Oct. 10–11, 2011, pp. 120–123. [7]. B. Kim et al., “Broadband Operation of Saturated Amplifier with High Efficiency,” IEEE Annu. Wireless Microw. Technol. Conf.,Tampa, FL, USA, June 6, 2014, pp. 1–4. [8]. K. Li et al., “A 40 W Ultra Broadband LDMOS Power Amplifier,” IEEE MTT-S Int. Microw. Symp., Phoenix, AZ, USA, May 17–22, 2015, pp. 1–4. [9]. Z. Dai et al., “A New Distributed Parameter Broadband Matching Method for Power Amplifier Via Real Frequency Technique,” IEEE Trans. Microw. Theory Techn., vol. 63, no. 2, Feb. 2015, pp.449–458. [10]. X. Ding and L. Zhang, “A High-Efficiency GaAs MMIC Power Amplifier for Multi-standard System,” IEEE Microw. Wireless Compon. Lett., vol. 26, no. 1, Jan. 2016, pp. 55–57. [11]. J. Kim et al., “Highly Efficient Envelope-Tracking Modulator over Wide Output Power Range for Dual-Mode Power Amplifier,” IDEC J. Integr. Circuits Syst., vol. 1, no. 1, 2015, pp.28–35. [12]. Z. Wang, “Demystifying Envelope Tracking: Use for HighEfficiency Power Amplifiers for 4G and Beyond,” IEEE Microw.Mag., vol. 16, no. 3, Apr. 2015, pp.106–129. [13]. A. Jundi, H. Sarbishaei, and S. Boumaiza, “An 85-W Multioctave Push-Pull GaN HEMT Power Amplifier for HighDfficiency Communication Applications at Microwave Frequencies,” IEEE Trans. Microw. Theory Techn., vol. 63, no. 11,Nov. 2015, pp. 3691–3700. [14]. D.Y.T. Wu, L. Zhao, and M. Szymanowski, “A 25 W, 2.3 to 2.7 GHz Wideband LDMOS Two-Stage RFIC Power Amplifier for Driver and Small- Cell Doherty Application,” European Microw. Integr. Circuits Conf., Paris, France, Sept. 7–8, 2015, pp. 258–261. Kỹ thuật điện tử N. T. Hà, , Đ. T. T. Biên, “Một số giải pháp thiết kế công suất cao tần dải rộng 25W.” 266 [15]. C.Q. Chen et al., “A 1.8–2.8 GHz Highly Linear Broadband Power Amplifier for LTE-A Application,” Progress Electromagn.Res. C, vol. 66, Apr. 2016, pp. 47–54. [16]. V. Camarchia et al., “The Doherty Power Amplifier: Review of Recent Solutions and Trends,” IEEE Trans. Microw. Theory Techn., vol. 63, no. 2, Feb. 2015, pp. 559–571. [17]. J. Xia et al., “A Broadband High-Efficiency Doherty Power Amplifier with Integrated Compensating Reactance,” IEEE Trans.Microw. Theory Techn., vol. 64, no. 7, July 2016, pp. 2014–2024. ABSTRACT A METHOD OF DESIGN AND CHARACTERIZATION OF 25W BROADBAND RF AMPLIFIER Radio frequency (RF) and microwave amplifier research have been largely focused on solid-state technology in recent years. This paper presents design and performance characterization of a 25W broadband modular solid-state amplifier. It includes architecture selection and design procedures based on circuit and ADS simulations for its building blocks like solid-state amplifier modules, stability, input and output matching networks. Key performance objectives such as output power, gain variation, power added efficiency are discussed for this amplifier for real-time operation. Characterization on the component level as well as system level of this amplifier serves useful data for RF designers working in communication, industrial, medical, defence, etc. Keywords: RF amplifier; Solid-state amplifier; Matching networks; Broadband. Nhận bài ngày 17 tháng 4 năm 2020 Hoàn thiện ngày 20 tháng 8 năm 2020 Chấp nhận đăng ngày 28 tháng 8 năm 2020 Địa chỉ: Viện Điện tử /Viện KH-CNQS. *Email: thanhhavdt@yahoo.com.vn.

File đính kèm:

mot_so_giai_phap_thiet_ke_mo_phong_dac_tuyen_cua_bo_khuech_d.pdf

mot_so_giai_phap_thiet_ke_mo_phong_dac_tuyen_cua_bo_khuech_d.pdf