Giáo trình Vi mạch số (Phần 2)

Mạch tạo xung vuông sử dụng cổng NAND.

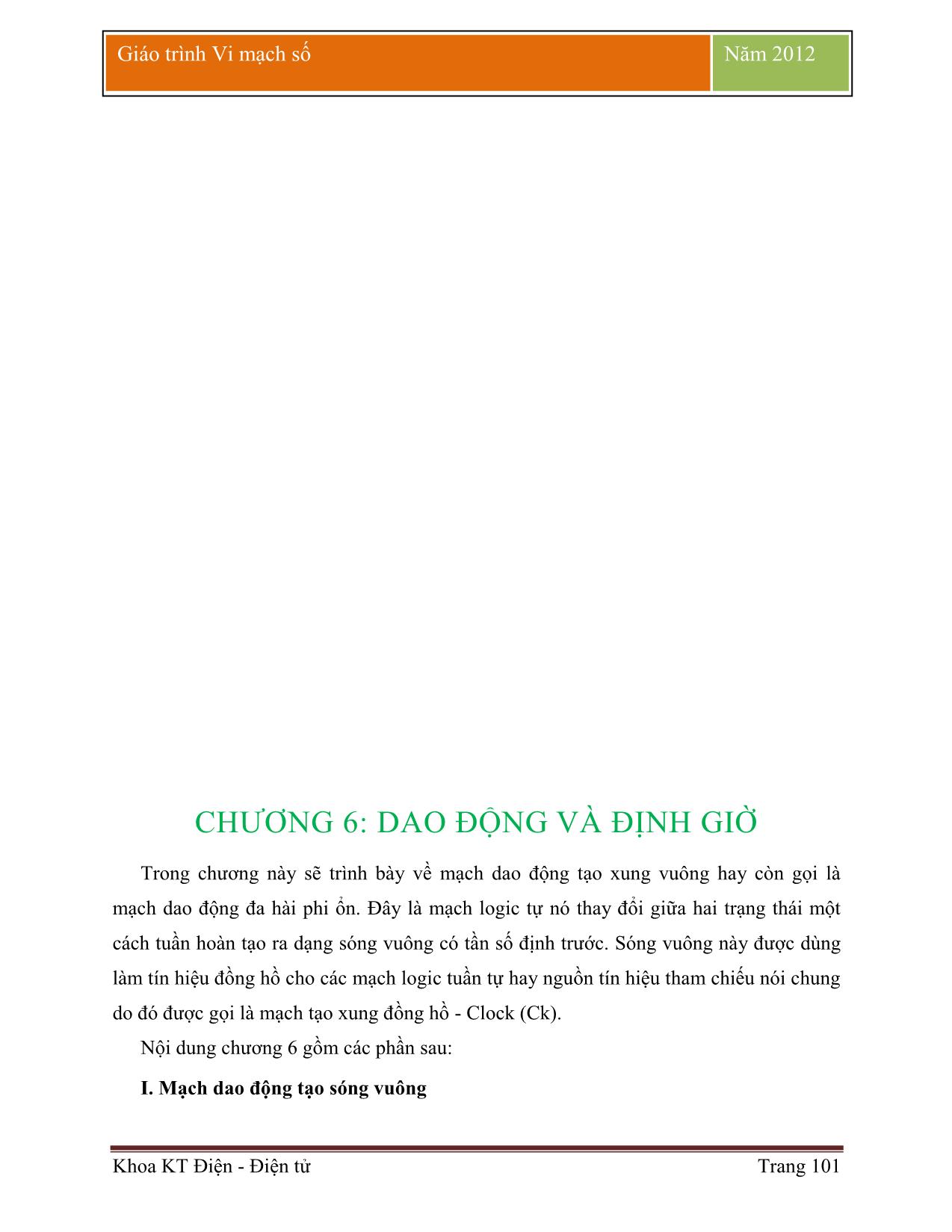

Xem mạch hình 6.1 gồm hai cổng NAND TTL N1 và N2 với tụ C1 và C2 trên đường

hồi tiếp chéo và điện trở R1, R2, ở ngõ vào. Ngõ vào còn lại của mỗi cổng NAND được

bỏ không hay nối lên VCC. Hai điện trở R1, R2, được chọn sao cho hai cổng dược phân

cực ở vùng tuyến tính giữa hai ngưỡng logic thấp và cao của cổng (ở cổng TTL ngưỡng

thấp là khoảng 0,9V, ngưỡng cao là khoảng 1,6V) để sự nạp, xả của hai tụ sẽ khiến ngõ

vào của hai cổng chuyển mạch giữa logic 0 và 1.

Giả sử ngõ vào của N1 xuống dưới ngưỡng thấp khiến ngõ ra Q=1, và tụ qua C2 khiến

ngõ vào của N2 lên 1 làm ngõ ra =0. Tụ C2 xả điện qua R2 xuống đất khiến điện thế tại

ngõ vào của N2 sụt dần đến lúc nào đó sẽ xuống dưới ngưỡng thấp tức có logic 0 làm ngõ

ra = 1 và qua tụ C1 khiến ngõ vào của N1 lên 1 dẩn đến ngõ ra Q= 0.

Lúc bấy giờ C1 xả điện qua R1 và R3 khiến điện thế tại ngõ vào của N1 sụt dần đến lúc

nào đó sẽ xuống ngưỡng thấp tức logic 0 làm ngõ ra Q= 1, v.v

Sự nạp xả như trên xảy ra liên tiếp và tuần hoàn tạo hai dạng sóng ngõ ra đảo pha

nhau, khi C1= C2= C và R1= R2= R thì dạng sóng ra đối xứng và có dạng là:

Các điện trở R1, R2, phải nhỏ (dưới 1KΩ) còn tụ C1, C2 từ vài chục pF đến khoảng

1000µF. khi dùng cổng CMOS các điện trở có thể đến 100K hoặc hơn nên mạch có thểKhoa KT Điện - Điện tử Trang 104

dao dộng ở tần số thấp hơn. Thường hai ngõ ra phải được đệm (ví dụ dùng hai cổng

NAND còn lại của 7400 để làm cổng đệm)

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Giáo trình Vi mạch số (Phần 2)

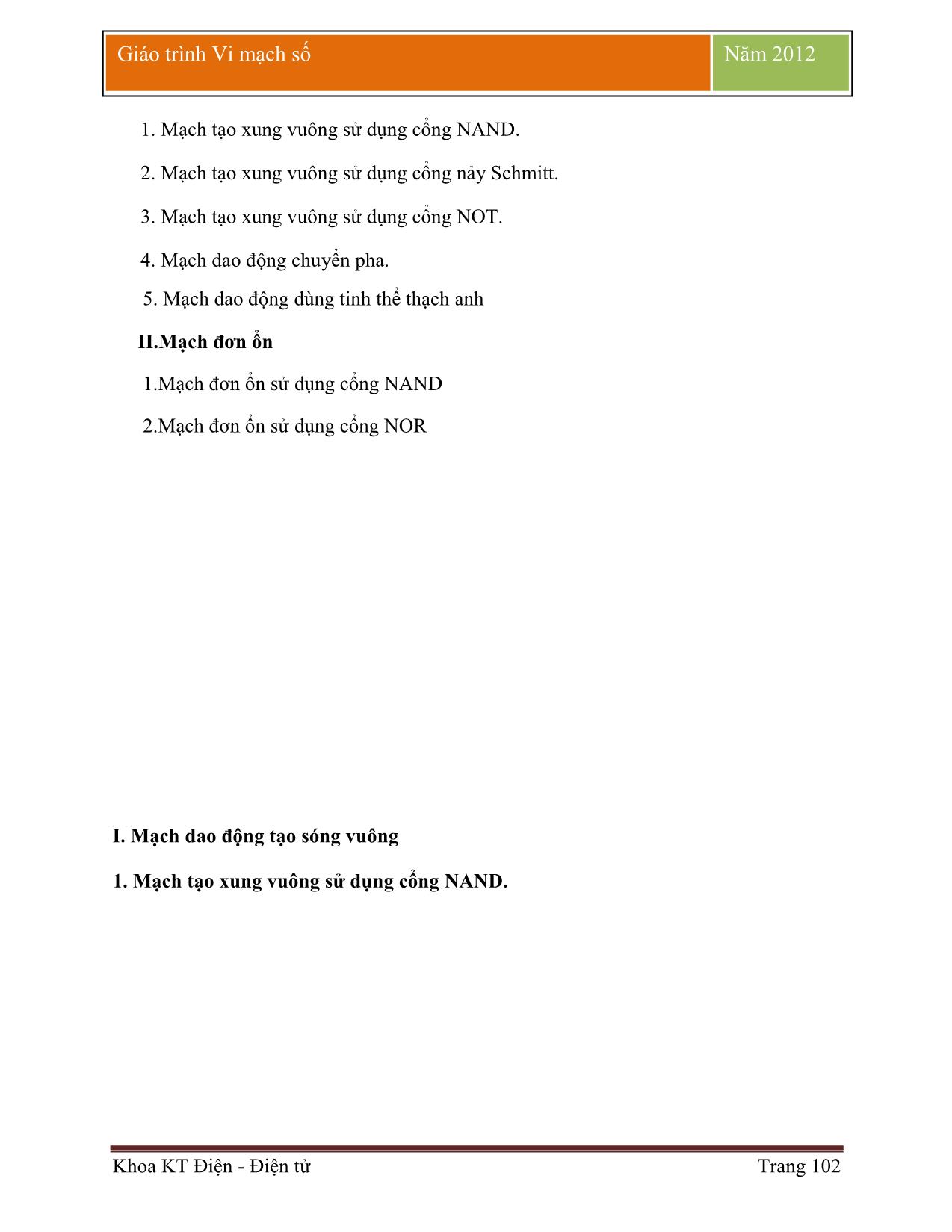

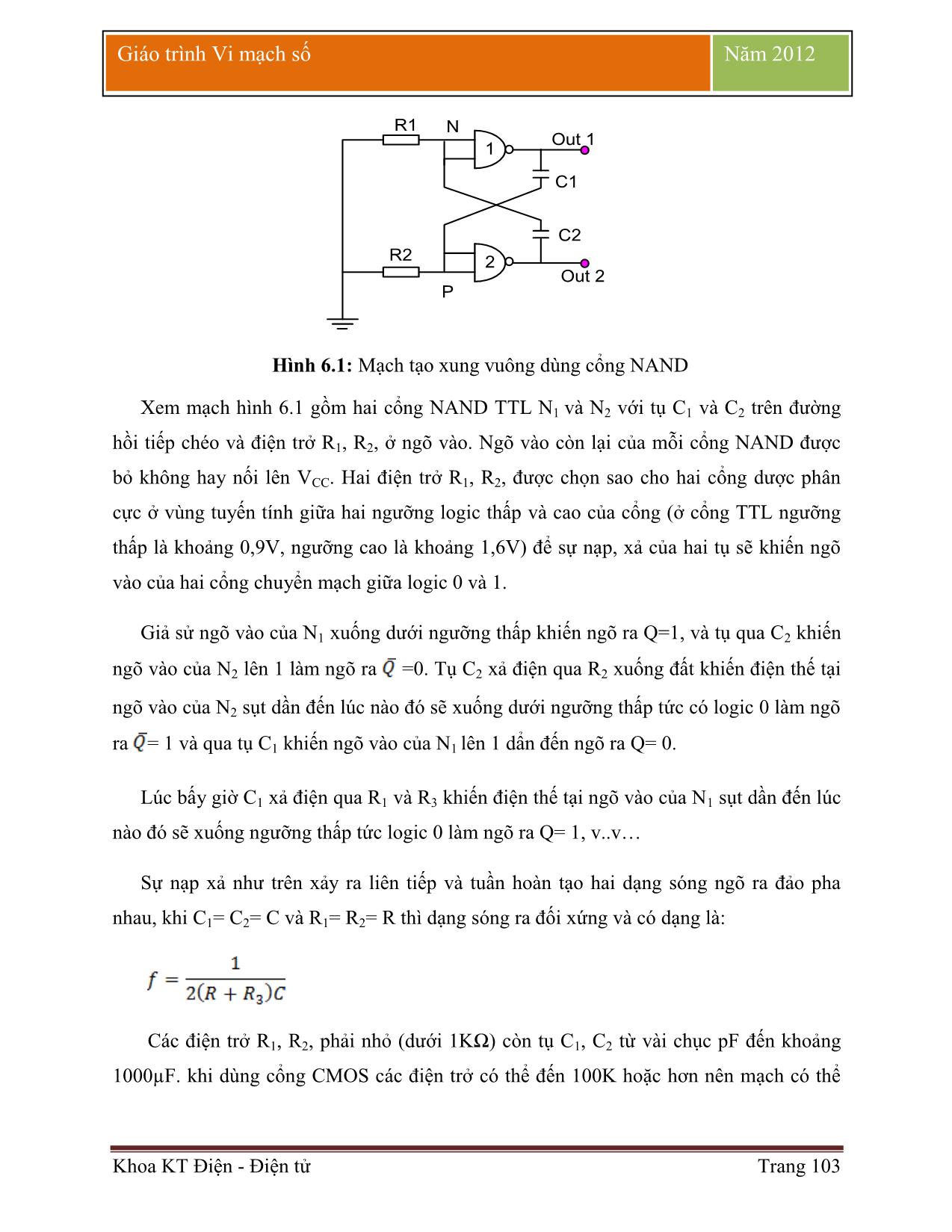

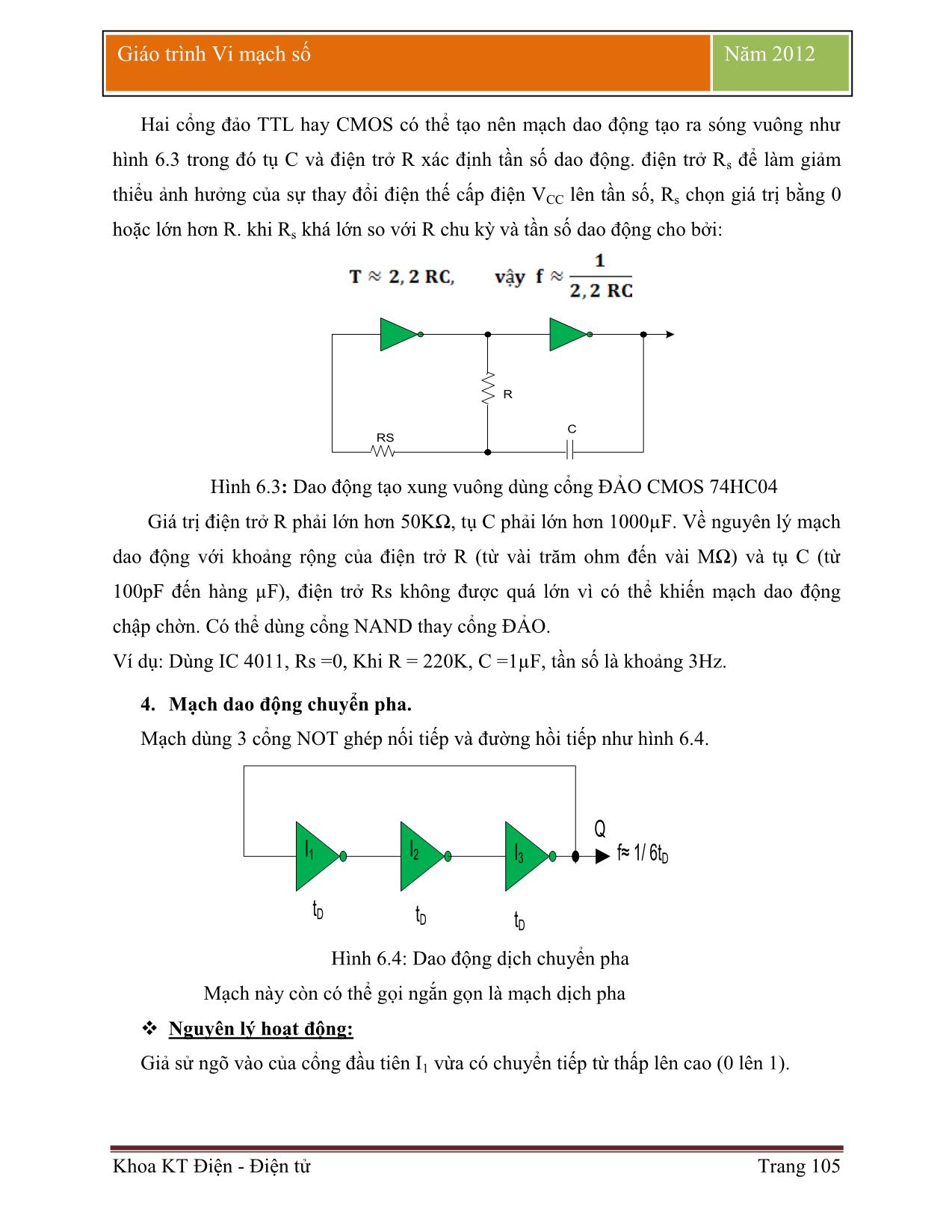

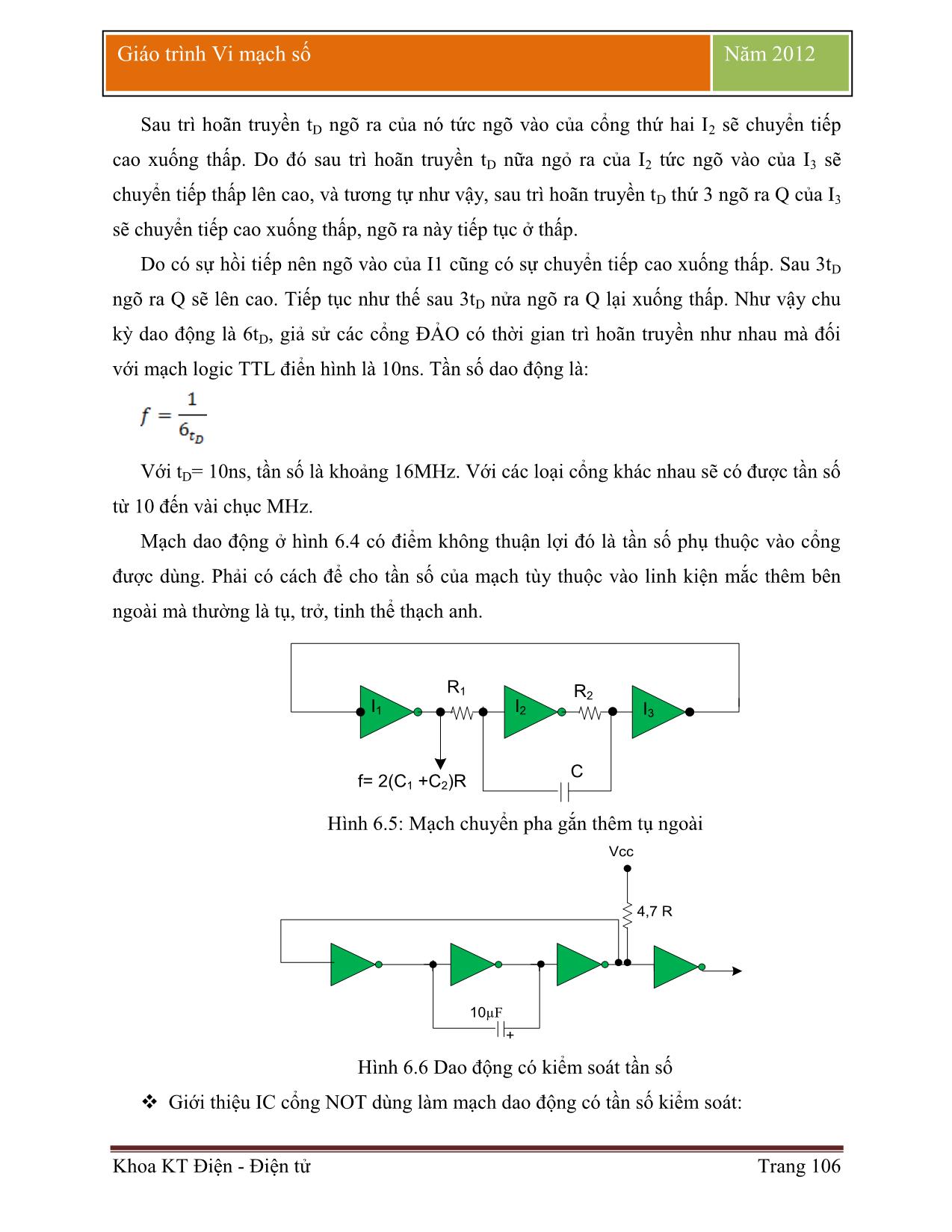

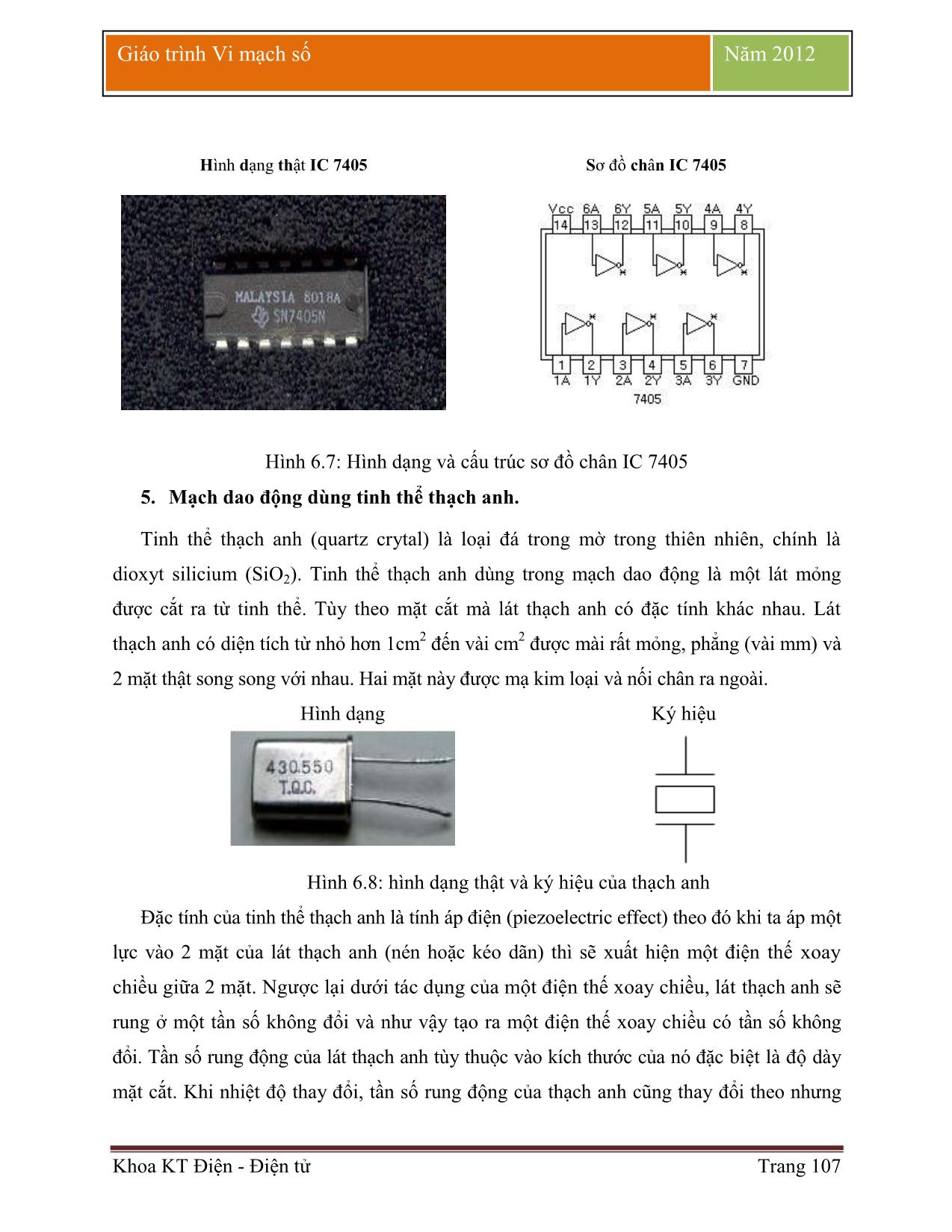

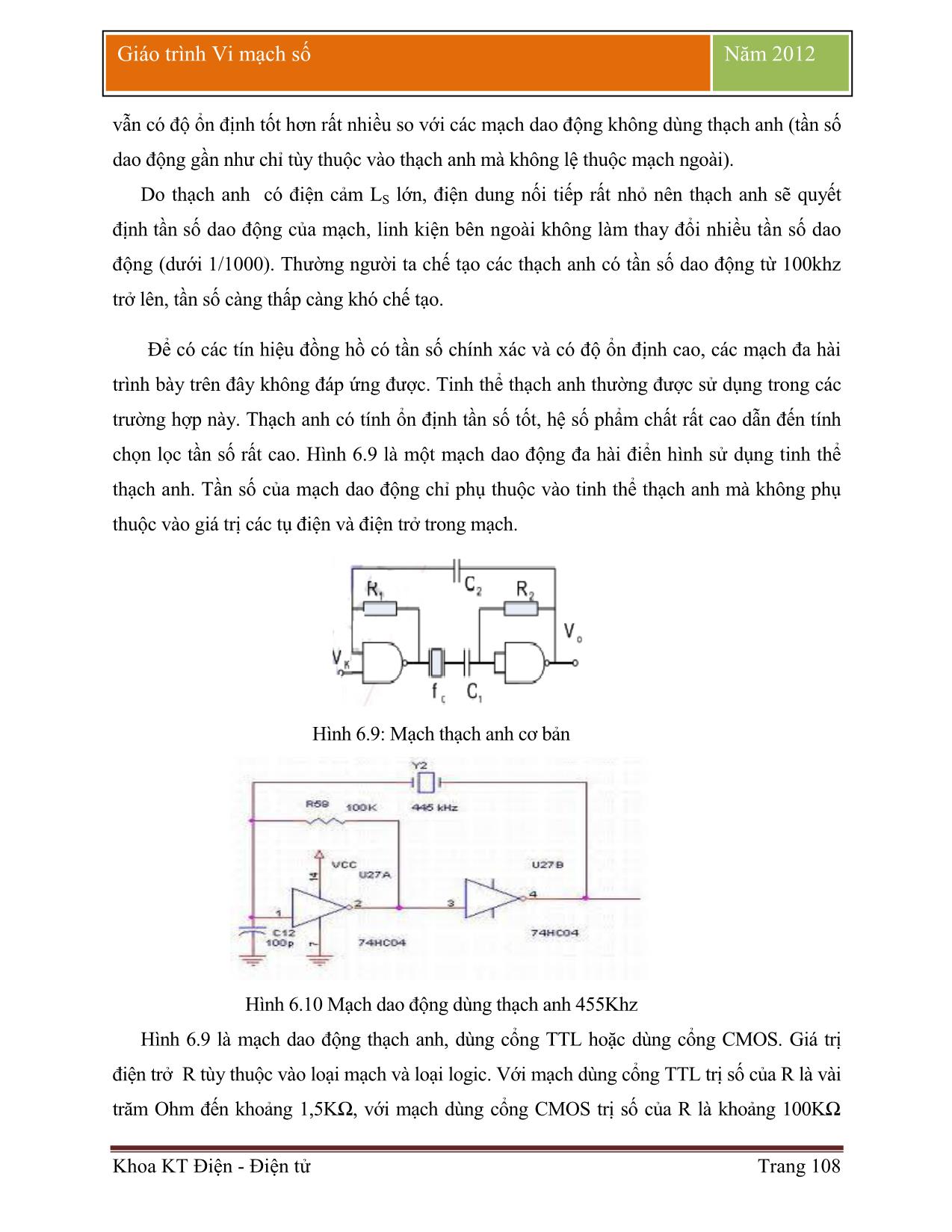

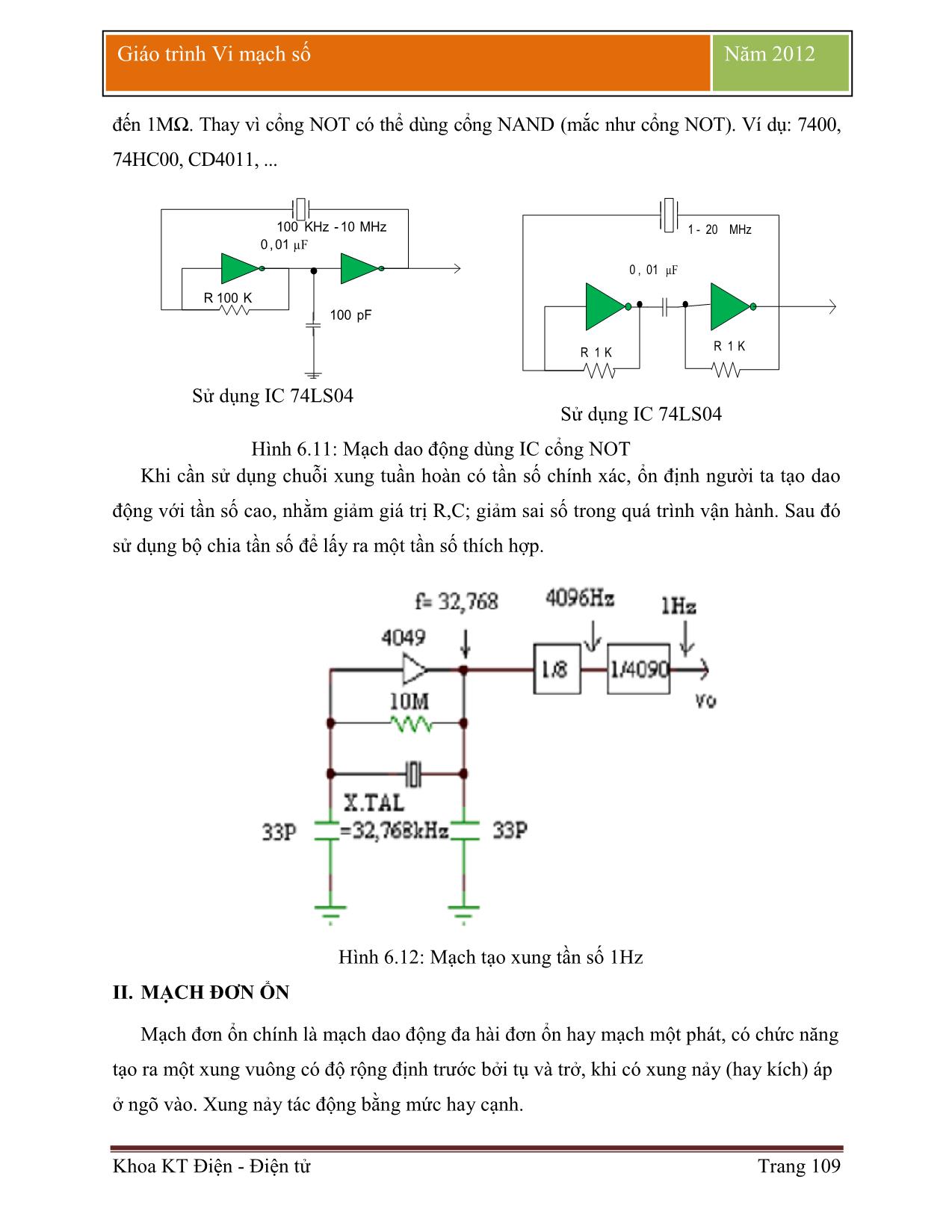

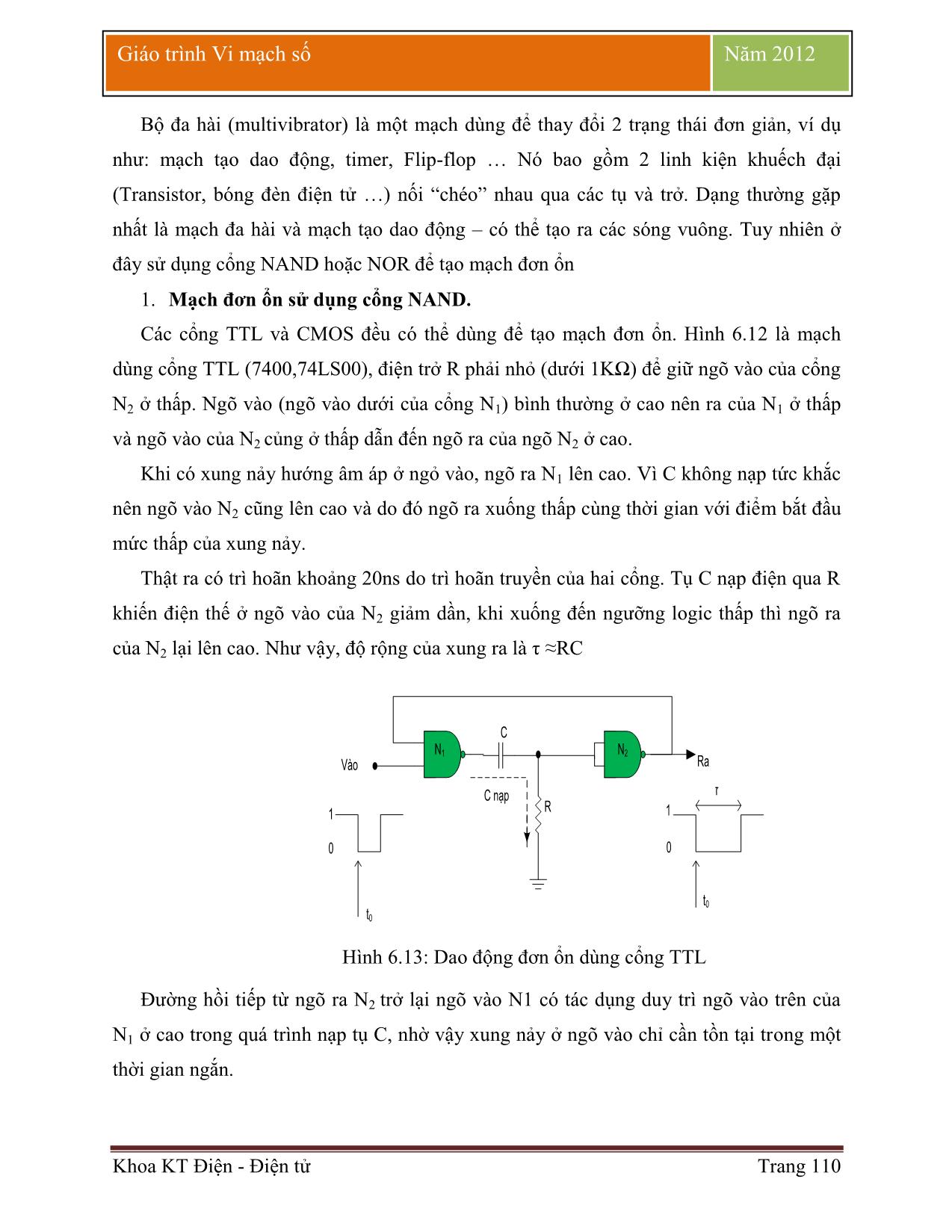

Khoa KT Điện - Điện tử Trang 101 Giáo trình Vi mạch số Năm 2012 CHƢƠNG 6: DAO ĐỘNG VÀ ĐỊNH GIỜ Trong chƣơng này sẽ trình bày về mạch dao động tạo xung vuông hay còn gọi là mạch dao động đa hài phi ổn. Đây là mạch logic tự nó thay đổi giữa hai trạng thái một cách tuần hoàn tạo ra dạng sóng vuông có tần số định trƣớc. Sóng vuông này đƣợc dùng làm tín hiệu đồng hồ cho các mạch logic tuần tự hay nguồn tín hiệu tham chiếu nói chung do đó đƣợc gọi là mạch tạo xung đồng hồ - Clock (Ck). Nội dung chƣơng 6 gồm các phần sau: I. Mạch dao động tạo sóng vuông Khoa KT Điện - Điện tử Trang 102 Giáo trình Vi mạch số Năm 2012 1. Mạch tạo xung vuông sử dụng cổng NAND. 2. Mạch tạo xung vuông sử dụng cổng nảy Schmitt. 3. Mạch tạo xung vuông sử dụng cổng NOT. 4. Mạch dao động chuyển pha. 5. Mạch dao động dùng tinh thể thạch anh II.Mạch đơn ổn 1.Mạch đơn ổn sử dụng cổng NAND 2.Mạch đơn ổn sử dụng cổng NOR I. Mạch dao động tạo sóng vuông 1. Mạch tạo xung vuông sử dụng cổng NAND. Khoa KT Điện - Điện tử Trang 103 Giáo trình Vi mạch số Năm 2012 1 2 Out 1 Out 2 R1 R2 C1 C2 N P Hình 6.1: Mạch tạo xung vuông dùng cổng NAND Xem mạch hình 6.1 gồm hai cổng NAND TTL N1 và N2 với tụ C1 và C2 trên đƣờng hồi tiếp chéo và điện trở R1, R2, ở ngõ vào. Ngõ vào còn lại của mỗi cổng NAND đƣợc bỏ không hay nối lên VCC. Hai điện trở R1, R2, đƣợc chọn sao cho hai cổng dƣợc phân cực ở vùng tuyến tính giữa hai ngƣỡng logic thấp và cao của cổng (ở cổng TTL ngƣỡng thấp là khoảng 0,9V, ngƣỡng cao là khoảng 1,6V) để sự nạp, xả của hai tụ sẽ khiến ngõ vào của hai cổng chuyển mạch giữa logic 0 và 1. Giả sử ngõ vào của N1 xuống dƣới ngƣỡng thấp khiến ngõ ra Q=1, và tụ qua C2 khiến ngõ vào của N2 lên 1 làm ngõ ra =0. Tụ C2 xả điện qua R2 xuống đất khiến điện thế tại ngõ vào của N2 sụt dần đến lúc nào đó sẽ xuống dƣới ngƣỡng thấp tức có logic 0 làm ngõ ra = 1 và qua tụ C1 khiến ngõ vào của N1 lên 1 dẩn đến ngõ ra Q= 0. Lúc bấy giờ C1 xả điện qua R1 và R3 khiến điện thế tại ngõ vào của N1 sụt dần đến lúc nào đó sẽ xuống ngƣỡng thấp tức logic 0 làm ngõ ra Q= 1, v..v Sự nạp xả nhƣ trên xảy ra liên tiếp và tuần hoàn tạo hai dạng sóng ngõ ra đảo pha nhau, khi C1= C2= C và R1= R2= R thì dạng sóng ra đối xứng và có dạng là: Các điện trở R1, R2, phải nhỏ (dƣới 1KΩ) còn tụ C1, C2 từ vài chục pF đến khoảng 1000µF. khi dùng cổng CMOS các điện trở có thể đến 100K hoặc hơn nên mạch có thể Khoa KT Điện - Điện tử Trang 104 Giáo trình Vi mạch số Năm 2012 dao dộng ở tần số thấp hơn. Thƣờng hai ngõ ra phải đƣợc đệm (ví dụ dùng hai cổng NAND còn lại của 7400 để làm cổng đệm). 2. Mạch tạo xung vuông sử dụng cổng nảy Schmitt. Các cổng nảy Schmitt IC7414 có thể đƣợc dùng nhƣ mạch dao động (Hình 6.2). Giả sử ngỏ vào của cổng vừa xuống thấp (logic 0) khiến ngõ ra Q vừa lên cao (logic 1) thì tụ C nạp qua điện trở R từ ngõ ra. Khi C nạp đến ngƣỡng logic cao thì ngõ vào lên cao khiến ngõ ra xuống thấp làm tụ xả điện vào ngõ ra. Khi C xả xuống đến ngƣỡng thấp logic ở ngõ ra đảo lại. Hình 6.2: Dao động tạo xung vuông dùng cổng nảy Schmitt Vì tụ C nạp và xả qua cùng điện trở R nên dạng sóng vuông ra đối xứng. Do ngƣỡng logic khác nhau nên tần số dao động của cổng TTL và cổng CMOS khác nhau. Tần số dao động còn bị ảnh hƣởng bởi điện trở ngõ ra của cổng và các yếu tố về nhiệt độ, v,v nên công thức ghi ở hình vẽ chỉ là xấp xỉ. Để ý là không đƣợc dùng điện trở trên giới hạn cho vì mạch sẽ không dao động Bảng 6.1 : Bảng tần số làm việc của IC74XX14 3. Mạch tạo xung vuông sử dụng cổng NOT. IC tần số 7414 0,8/R (R<500Ω) 74LS14 0,8/R (R<2KΩ) 74HC14 1,2/R (R<10MΩ) Khoa KT Điện - Điện tử Trang 105 Giáo trình Vi mạch số Năm 2012 Hai cổng đảo TTL hay CMOS có thể tạo nên mạch dao động tạo ra sóng vuông nhƣ hình 6.3 trong đó tụ C và điện trở R xác định tần số dao động. điện trở Rs để làm giảm thiểu ảnh hƣởng của sự thay đổi điện thế cấp điện VCC lên tần số, Rs chọn giá trị bằng 0 hoặc lớn hơn R. khi Rs khá lớn so với R chu kỳ và tần số dao động cho bởi: RS R C Hình 6.3: Dao động tạo xung vuông dùng cổng ĐẢO CMOS 74HC04 Giá trị điện trở R phải lớn hơn 50KΩ, tụ C phải lớn hơn 1000µF. Về nguyên lý mạch dao động với khoảng rộng của điện trở R (từ vài trăm ohm đến vài MΩ) và tụ C (từ 100pF đến hàng µF), điện trở Rs không đƣợc quá lớn vì có thể khiến mạch dao động chập chờn. Có thể dùng cổng NAND thay cổng ĐẢO. Ví dụ: Dùng IC 4011, Rs =0, Khi R = 220K, C =1µF, tần số là khoảng 3Hz. 4. Mạch dao động chuyển pha. Mạch dùng 3 cổng NOT ghép nối tiếp và đƣờng hồi tiếp nhƣ hình 6.4. tD tD tD I3I2I1 Q f≈ 1/ 6tD Hình 6.4: Dao động dịch chuyển pha Mạch này còn có thể gọi ngắn gọn là mạch dịch pha Nguyên lý hoạt động: Giả sử ngõ vào của cổng đầu tiên I1 vừa có chuyển tiếp từ thấp lên cao (0 lên 1). Khoa KT Điện - Điện tử Trang 106 Giáo trình Vi mạch số Năm 2012 Sau trì hoãn truyền tD ngõ ra của nó tức ngõ vào của cổng th ... gic ..................................... 38 BÀI TẬP CHƢƠNG 2 ...................................................................................................... 40 Chƣơng 3: CỔNG LOGIC TTL ........................................................................................ 41 1. Mạch logic TTL. ......................................................................................................... 41 2. Các loại TTL. .............................................................................................................. 47 3. Đặc tính điện của cổng TTL. ...................................................................................... 49 4. Số ngỏ ra. .................................................................................................................... 52 5. TTL Cực Thu Hở Và TTL 3 Trạng Thái. ...................................................................... 53 6. Một Số Loại Đệm Thúc. ................................................................................................ 58 7. Giao tiếp logic với tải DC, AC. .................................................................................. 59 BÀI TẬP CHƢƠNG 3 ...................................................................................................... 61 Chƣơng 4 : CỔNG LOGIC CMOS. .................................................................................. 62 1.Transistor MOSFET ...................................................................................................... 64 2. Các loại IC logic CMOS ................................................................................................ 66 2.1 Loại 4000A, 4000B, 4500. .......................................................................................... 66 2.2 Loại 74C. ..................................................................................................................... 67 2.3 Loại 74HC, 74HCT (High Speed CMOS). ................................................................. 67 3. Đặc tính điện của logic CMOS ................................................................................... 69 3.1 Điện thế cấp điện ......................................................................................................... 69 3.2 Các điện thế logic ở ngõ vào ....................................................................................... 70 3.3 Các điện thế logic ở ngõ ra .......................................................................................... 71 3.4 Dòng điện vào và dòng điện ra .................................................................................... 72 3.5 Số tỏa ra ...................................................................................................................... 72 4. Giao tiếp mạch logic với DC,AC. .............................................................................. 73 4.1 Giao tiếp với tải DC ..................................................................................................... 73 Khoa KT Điện - Điện tử Trang 203 Giáo trình Vi mạch số Năm 2012 4.2 Giao tiếp với tải AC ..................................................................................................... 77 BÀI TẬP CHƢƠNG 4 ...................................................................................................... 79 CHƢƠNG 5:MẠCH TUẦN TỰ FLIP-FLOP,VÀ GHI DỊCH ......................................... 80 1.1 Khái niệm: .................................................................................................................. 81 1.2 Phân loại: .................................................................................................................... 82 1.3 Phƣơng pháp kích: ....................................................................................................... 82 2. FLIP-FLOP R-S ............................................................................................................. 83 2.1 RS-FF không đồng bộ.................................................................................................. 83 2.2 RS - FF đồng bộ........................................................................................................... 85 3.FLIP-FLOP JK ............................................................................................................... 88 3.1 Cấu trúc: ...................................................................................................................... 88 3.2 Kí hiệu và bảng trạng thái: .......................................................................................... 89 3.3 Ứng dụng của JK FF .................................................................................................... 91 3.4 Giới thiệu họ IC FF JK: ............................................................................................... 91 4. FLIP-FLOP T ................................................................................................................ 92 4.1 Cấu trúc: ...................................................................................................................... 92 4.2 Kí hiệu và bảng trạng thái FF-T .................................................................................. 93 4.3 Dạng sóng ngỏ ra Q (giản đồ thời gian) ...................................................................... 93 5.FLIP-FLOP D và mạch ghi: ........................................................................................... 93 5.1 Cấu trúc : ..................................................................................................................... 93 5.2 Dạng sóng tín hiệu Q theo D ( giản đồ thời gian) ....................................................... 94 5.3 Mạch chốt giữ liệu ...................................................................................................... 95 5.4 Giới thiệu họ IC FF-D: ................................................................................................ 95 BÀI TẬP CHƢƠNG 5: ..................................................................................................... 99 CHƢƠNG 6: DAO ĐỘNG VÀ ĐỊNH GIỜ ............................................................... 101 I. Mạch dao động tạo sóng vuông ................................................................................... 102 1. Mạch tạo xung vuông sử dụng cổng NAND. .............................................................. 102 2. Mạch tạo xung vuông sử dụng cổng nảy Schmitt. ..................................................... 104 3. Mạch tạo xung vuông sử dụng cổng NOT. .............................................................. 104 Khoa KT Điện - Điện tử Trang 204 Giáo trình Vi mạch số Năm 2012 4. Mạch dao động chuyển pha. ..................................................................................... 105 5. Mạch dao động dùng tinh thể thạch anh. .................................................................. 107 II. MẠCH ĐƠN ỔN ...................................................................................................... 109 1. Mạch đơn ổn sử dụng cổng NAND. ......................................................................... 110 2. Mạch đơn ổn sử dụng cổng NOR. ............................................................................ 111 BÀI TẬP CHƢƠNG 6 .................................................................................................... 112 CHƢƠNG 7: MẠCH TỔ HỢP MSI ............................................................................... 112 1. Mạch mã hóa. ........................................................................................................... 113 1.1 Mã hóa 8 sang 3 ........................................................................................................ 114 1.2 Mạch mã hóa 10 đƣờng sang 4 đƣờng. .................................................................... 115 1.3 Mã hóa ƣu tiên. ......................................................................................................... 116 2. Mạch giải mã . .......................................................................................................... 118 2.1 Giải mã 2 sang 4 ....................................................................................................... 118 2.2 Giải mã 3 sang 8 ....................................................................................................... 119 2.3 Mạch giải mã BCD sang thập phân. .......................................................................... 121 2.4 Giải mã BCD sang led 7 đoạn ................................................................................... 123 3. Mạch đa hợp/ Chọn dữ liệu. ..................................................................................... 129 3.1 Mạch dồn kênh 4 sang 1 ............................................................................................ 131 3.2 Một số IC dồn kênh hay dùng ................................................................................... 132 4. Mạch giải đa hợp / phân phát dữ liệu /Giải mã ....................................................... 134 4.1 Mạch giải đa hợp. ...................................................................................................... 134 4.2 Mạch phân dữ liệu từ 1 sang 4 .................................................................................. 135 4.3 Mạch giải đa hợp hoạt động nhƣ mạch giải mã ........................................................ 137 5. Ứng dụng của mạch đa hợp, giải đa hợp. ................................................................. 141 5.1 Mở rộng kênh ghép .................................................................................................... 141 5.2 Chuyển đổi song song sang nối tiếp: ......................................................................... 142 5.3 Dùng dồn kênh để thiết kế tổ hợp: ............................................................................ 143 5.4 Dùng mạch tách kênh thiết kế mạch logic................................................................ 144 5.5 Chia sẻ đƣờng truyền ................................................................................................. 145 Khoa KT Điện - Điện tử Trang 205 Giáo trình Vi mạch số Năm 2012 BÀI TẬP CHƢƠNG 7 .................................................................................................... 148 CHƢƠNG 8: BỘ NHỚ ROM VÀ RAM. ....................................................................... 149 1. Khái niệm : ............................................................................................................... 150 1.1 Đặc điểm bộ nhớ : ..................................................................................................... 150 1.2 Các thuật ngữ quan trọng:......................................................................................... 151 1.3 Hoạt động và cấu trúc bộ nhớ ................................................................................... 152 1.4 Giao tiếp với CPU máy tính (Central Processing Unit) ........................................... 154 2. Cấu tạo của ROM. .................................................................................................... 155 2.1 Khái niệm: ................................................................................................................ 155 2.2 Cấu trúc bên trong của ROM .................................................................................... 156 2.3 Thông số của ROM : ................................................................................................ 158 2.4 Các loại ROM đặc trƣng: .......................................................................................... 159 3. Cấu tạo của RAM (Read Access Memory) .............................................................. 164 3.1 Khái niệm : ............................................................................................................... 164 3.2 Cấu trúc và hoạt động của RAM : ............................................................................ 165 3.3 Ý nghĩa và thông số kỹ thuật .................................................................................... 166 3.4 Các loại RAM ........................................................................................................... 167 3.5 Dồn kênh địa chỉ - Address Multiplexing (ghép địa chỉ) .......................................... 175 3.6 Biểu hiện khi hỏng RAM .......................................................................................... 177 4. Các loại bộ nhớ khác. ............................................................................................... 178 BÀI TẬP CHƢƠNG 8 .................................................................................................... 180 Chƣơng 9: ỨNG DỤNG BỘ CHUYỂN ĐỔI SỐ - TƢƠNG TỰ; TƢƠNG TỰ - SỐ.... 181 1. Chuyển đổi tƣơng tự – số. ........................................................................................ 182 1.1 Khái niệm: ................................................................................................................ 182 1.2 Các thông số kỹ thuật của ADC : .............................................................................. 183 1.3 Mạch lấy mẫu và giữ (sample and Hold – SH) ......................................................... 183 1.4 Các loại ADC: .......................................................................................................... 184 2. Chuyển đổi số sang tƣơng tự (ADC) ........................................................................ 188 2.1 Khái niệm : ............................................................................................................... 188 Khoa KT Điện - Điện tử Trang 206 Giáo trình Vi mạch số Năm 2012 2.2. Các thông số cơ bản :................................................................................................ 188 2.2 Các loại DAC : ........................................................................................................ 191 2.2.1 DAC dùng điện trở có trọng số nhị phân (mạng điện trở) : ................................... 191 2.2.2 DAC R/2R ladder ( DAC kiểu bậc thang): ......................................................... 193 2.2.3 DAC với đầu ra dòng : ....................................................................................... 195 2.2.4 DAC điện trở hình T: ......................................................................................... 196 BÀI TẬP CHƢƠNG 9 .................................................................................................... 199 TÀI LIỆU THAM KHẢO ............................................................................................... 200

File đính kèm:

giao_trinh_vi_mach_so_phan_2.pdf

giao_trinh_vi_mach_so_phan_2.pdf