Giáo trình Vi mạch số (Phần 1)

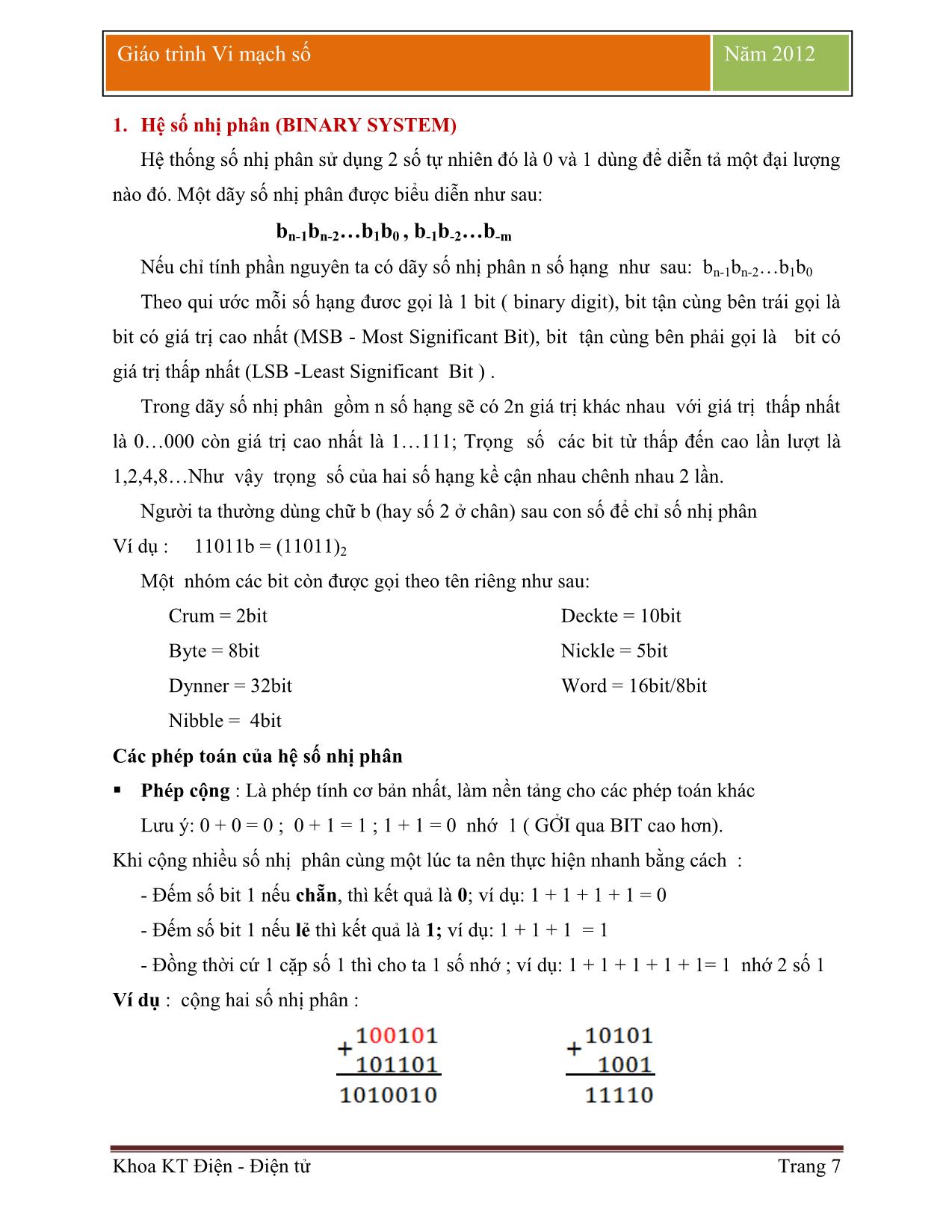

Hệ số nhị phân (BINARY SYSTEM)

Hệ thống số nhị phân sử dụng 2 số tự nhiên đó là 0 và 1 dùng để diễn tả một đại lƣợng

nào đó. Một dãy số nhị phân đƣợc biểu diễn nhƣ sau:

bn-1bn-2 b1b0 , b-1b-2 b-m

Nếu chỉ tính phần nguyên ta có dãy số nhị phân n số hạng nhƣ sau: bn-1bn-2 b1b0

Theo qui ƣớc mỗi số hạng đƣơc gọi là 1 bit ( binary digit), bit tận cùng bên trái gọi là

bit có giá trị cao nhất (MSB - Most Significant Bit), bit tận cùng bên phải gọi là bit có

giá trị thấp nhất (LSB -Least Significant Bit ) .

Trong dãy số nhị phân gồm n số hạng sẽ có 2n giá trị khác nhau với giá trị thấp nhất

là 0 000 còn giá trị cao nhất là 1 111; Trọng số các bit từ thấp đến cao lần lƣợt là

1,2,4,8 Nhƣ vậy trọng số của hai số hạng kề cận nhau chênh nhau 2 lần.

Ngƣời ta thƣờng dùng chữ b (hay số 2 ở chân) sau con số để chỉ số nhị phân

Ví dụ : 11011b = (11011)2

Một nhóm các bit còn đƣợc gọi theo tên riêng nhƣ sau:

Crum = 2bit

Byte = 8bit

Dynner = 32bit

Nibble = 4bit

Deckte = 10bit

Nickle = 5bit

Word = 16bit/8bit

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Giáo trình Vi mạch số (Phần 1)

ỦY BAN NHÂN DÂN TP. HỒ CHÍ MINH TRƢỜNG CAO ĐẲNG GIAO THÔNG VẬN TẢI ---------- GIÁO TRÌNH TRÌNH ĐỘ: CAO ĐẲNG Thực hiện: 1.ThS. Nguyễn Đức Lợi (Chủ nhiệm) 2.ThS. Nguyễn Trọng Trung 3. KS. Võ Minh Trí Lưu hành nội bộ, 09 / 2012 VI MẠCH SỐ Khoa KT Điện - Điện tử Trang 3 Giáo trình Vi mạch số Năm 2012 LỜI NÓI ĐẦU Trong thời đại phát triển mạnh về công nghệ số nhƣ hiện nay, việc truyền dẫn thông tin thu phát đều cần đƣợc mã hóa và tích hợp cao nhằm tiết kiệm băng tần, hạn chế nhiễu, giảm thiểu rủi ro nhờ tính bảo mật tốt. Vi mạch số là môn học hữu ích cho sinh viên khối kỹ thuật nhất là sinh viên ngành điện - điện tử. Mọi sinh viên ngành điện đều cần nắm vững cơ sở lý thuyết để tạo nền tảng cho việc học tiếp các môn chuyên ngành nhƣ vi xử lý. Từ đó có thể thiết kế các mạch ứng dụng nhƣ mạch đồng hồ, mạch đếm sản phẩm, mạch đèn giao thông, mạch quang báo Trên thị trƣờng hiện nay tài liệu về vi mạch số khá nhiều, tuy nhiên lại đề cập đến nhiều mảng nội dung khác nhau, mỗi sách viết một kiểu, điều này gây không ít khó khăn cho sinh viên trong việc tìm kiếm một tài liệu phù hợp. Nhằm giúp sinh viên Khoa Điện - Điện tử của Trƣờng Cao đẳng Giao thông vận tải TP. Hồ Chí Minh có một cuốn tài liệu tham khảo học tập theo sát chƣơng trình và mục tiêu đào tạo của Trƣờng, đƣợc sự quan tâm của Trƣởng khoa, Ban Giám hiệu, các Thầy, Cô khoa KT Điện - Điện tử tiến hành biên soạn cuốn “Giáo trình Vi mạch số”. Nội dung cuốn giáo trình vi mạch số gồm 9 chƣơng đƣợc giảng dạy trong thời lƣợng 60 tiết. Trong đó chủ biên Thầy Nguyễn Trọng Trung biên soạn 3 chƣơng đầu. Chƣơng 1: Hệ thống số và mã số. Giới thiệu về các cơ số 2,8,10,16 và phép tính, chuyển đổi giữa các cơ số, đồng thời trình bày về mã BCD , mã ASSCI ứng dụng trong máy tính, giải mã Led 7 đoạn Chƣơng 2 : Cổng logic và đại số BOOLE Chƣơng này lại cho biết về ký hiệu, phƣơng trình các cổng nhƣ NOT, AND, OR từ đó dùng phép toán đại số BOOLE hoặc lập bìa Karnaugh để rút gọn các hàm logic nhằm đơn giản hóa sơ đồ. Khoa KT Điện - Điện tử Trang 4 Giáo trình Vi mạch số Năm 2012 Chƣơng 3 : Cổng logic TTL Trong chƣơng này trình bày đặc điểm cấu tạo của các cổng logic với công nghệ Transistor – Transistor. Qua đó xác định tầm giá trị điện áp ở mức cao, mức thấp cũng nhƣ cho biết cách giao tiếp với tải AC / DC. Nội dung ba chƣơng tiếp theo đƣợc biên soạn bởi Thầy Võ Minh Trí Chƣơng 4 : Cổng logic CMOS Cho biết các đặc tính điện của công nghệ CMOS, có nhiều ƣu điểm nổi bậc về khả năng chống nhiễu cũng nhƣ khả năng giao tiếp tải AC / DC Chƣơng 5: Mạch tuần tự Flip-Flop và ghi dịch. Trình bày về một mạch điện có đặc tính nhớ nghĩa là ngỏ ra phụ thuộc vào trạng thái ngỏ vào và trạng thái ngỏ ra trƣớc đó, đó là các mạch RS – FF; JK – FF; T – FF; D – FF đồng thời cho biết các ứng dụng của nó trong việc thiết kế mạch đếm, thanh ghi dịch Chƣơng 6: Dao động và Định giờ Trong chƣơng sẽ cho chúng ta các sơ đồ mạch tạo xung dao động, đặc biệt là các mạch tạo xung vuông dùng làm xung kích, xung đồng hồ ( xung Clock) và mạch đơn ổn dùng các cổng logic nhƣ NAND , NOR Tiếp theo, ba chƣơng cuối đƣợc biên soạn bởi Thầy Nguyễn Đức Lợi Chƣơng 7: Mạch tổ hợp MSI Giới thiệu về mạch tổ hợp từ các cổng logic, đặc tính ngỏ ra chỉ phụ thuộc vào ngỏ vào, qua đó giúp sinh viên tìm hiểu về cách mã hóa, giải mã một tín hiệu trong việc truyền thông tin, kết hợp với đó là các mạch đa hợp (ghép kênh) và giải đa hợp ( phân kênh). Chƣơng 8: Bộ nhớ ROM và RAM. Khoa KT Điện - Điện tử Trang 5 Giáo trình Vi mạch số Năm 2012 Chƣơng này giới thiệu về một bộ nhớ dùng lƣu trữ và truy xuất thông tin, nhằm giúp sinh viên xác định đƣợc dung lƣợng bộ nhớ, cách thức ghi/ đọc dữ liệu cũng nhƣ phƣơng pháp mở rộng bộ nhớ. Qua đó trình bày đặc điểm của các bộ nhớ nhƣ MROM; PROM; EPROM; EEPROM, các loại RAM tĩnh, RAM động và cách làm tƣơi RAM Chƣơng 9: Ứng dụng bộ chuyển đổi số – tƣơng tự, tƣơng tự – số Đây là nội dung quan trọng trong việc xử lý tín hiệu, trong tự nhiên các tín hiệu nhƣ nhiệt độ, âm thanh, ánh sáng, hình ảnh là các tín hiệu tƣơng tự việc xử lý rất phức tạp trong việc thiết kế mạch do đó nó đƣợc chuyển sang tín hiệu số, sau đó đƣợc biến đổi ngƣợc lại thành tín hiệu ban đầu. Chƣơng này giúp sinh viên xác định đƣợc các thông số đặc trƣng của mạch ADC/ DAC, từ đó tính toán, thiết kế mạch theo yêu cầu. Trong quá trình thực hiện cuốn giáo trình vi mạch số nhóm tác giả có tham khảo tài liệu từ các trƣờng đại học trong khu vực và cũng nhận đƣợc khá nhiều đóng góp ý kiến từ các đồng nghiệp nhằm giúp giáo trình hoàn thiện hơn, nhóm tác giả chân thành cảm ơn. Do Trƣờng vừa chuyển lên cao đẳng và đối tƣợng sinh viên cao đẳng ngành điện đến nay chỉ là khóa thứ 2, nên cuốn giáo trình không tránh khỏi thiếu xót, nhóm tác giả mong đón nhận sự góp ý từ Hội đồng và các bạn đọc gần xa. TP Hồ Chí Minh, tháng 12 năm 2012 Nhóm tác giả. Khoa KT Điện - Điện tử Trang 6 ... của FF đồng bộ thay đổi trạng thái khi có sự tác động của xung Clock (xung CK) còn gọi là các xung kích. Xung đồng hồ (Clock) đƣợc diễn tả bằng một xung vuông, thƣờng là một chuối xung vuông, do vậy để kích FF ta có thể kích mức cao (mức 1), mức thấp (mức 0) hoặc kích bằng cạnh lên (sƣờn lên, sƣờn dƣơng) hay cạnh xuống (sƣờn xuống, sƣờn âm) điều này hoàn toàn phụ thuộc vào cấu trúc của FF. Hình 5.3 Phƣơng pháp kích bằng xung Clock Hình 5.4 : Ký hiệu các kiểu kích FF bằng xung CK Sƣờn lên và mức logic 1 có mối quan hệ với nhau, vì vậy mạch tạo sƣờn lên là mạch cải tiến của mạch tác động theo mức logic 1. Khoa KT Điện - Điện tử Trang 83 Giáo trình Vi mạch số Năm 2012 Sƣờn lên thực chất là một xung dƣơng, có thời gian tồn tại rất ngắn. Để cải tiến các FF tác động theo mức logic 1 thành FF tác động theo sƣờn lên ta mắc vào trƣớc FF đó một mạch tạo sƣờn lên. 1 2 3 4 Ck S y R S R Q Q Hình 5.5: FF có tín hiệu Ck điều khiển theo sƣờn lên 2. FLIP-FLOP R-S 2.1 RS-FF không đồng bộ Dạng 1: RSFF không đồng bộ dùng cổng NOR S R Q Q2 1 Hình 5.6 RSFF không đồng bộ cổng NOR Bảng 5.1: bảng trạng thái RS -FF Dựa vào bảng chân trị cuả cổng NOR để giải thích hoạt động của sơ đồ mạch này: -S=0,R=1 Q=0.Q=0 hồi tiếp về cổng NOR 2 nên cổng NOR 2 có hai ngõ vào bằng 0 Q =1.Vậy Q=0 và Q =1. -S=1,R=0 Q =0. Q =0 hồi tiếp về cổng NOR 1 nên cổng NOR 1 có hai ngõ vào =0. Q=1.Vậy,Q=1 và Q =0 -Giả sử ban đầu S=0,R=1 Q=0 và Q =1. Nếu tín hiệu ngõ vào thay đổi thành S=0,R=0(R chuyển từ 1 0) ta có: +S=0 và Q=0 Q =1 +R=0 và Q =1 Q=0 RSFF giữ nguyên trạng thái cũ trƣớc đó. S R Q 0 0 Q0 0 1 0 1 0 1 1 1 X Khoa KT Điện - Điện tử Trang 84 Giáo trình Vi mạch số Năm 2012 -Giả sử ban đầu S=1,R=0 Q=1 và Q =0 Nếu tín hiệu ngõ vào thay đổi thành: R=0,S=0 (S chuyển từ 1 0) ta có: +R=0 và Q =0 Q=1 +S=0 và Q=1 Q =0 RSFF giữ nguyên trạng thái cũ trƣớc đó. Dạng 2: RSFF không đồng bộ dùng cổng NAND S R Q Q2 1 Hình 5.7: RSFF không đồng bộ cổng NAND Bảng 5.2 Bảng trạng thái RS-FF. Dựa vào bảng chân trị của cổng NAND: 0 1 1 0 i i x x y Ta có: - 0, 1S R Q=1.Q=1 hồi tiếp về cổng NAND 2 nên cổng NAND 2 có hai ngõ vào bằng 1 vậy Q =0. - 0, 1 1, 1S R Q Q hồi tiếp về cổng NAND 1 nên cổng NAND 1 có hai ngõ vào bằng 1 vậy Q=0. - 0 1S R Q Q đây là trạng thái cấm. - 1:S R Giả sử trạng thái trƣớc đó có Q=1, 0Q hồi tiếp về cổng NAND 1 nên cổng NAND 1 có một ngõ vào bằng 0 Vậy Q=1 RSFF giữ nguyên trạng thái cũ. *Nhƣ vậy gọi là FF không đồng bộ bởi vì chỉ cần một trong hai ngõ vào S hay R thay đổi thì ngõ ra cũng thay đổi theo. Về mặt kí hiệu,các RSFF không đồng bộ đƣợc kí hiệu nhƣ sau: S R Q 0 0 X 0 1 1 1 0 0 1 1 Q0 Khoa KT Điện - Điện tử Trang 85 Giáo trình Vi mạch số Năm 2012 S R Ck Q Q R Q S S Q R a)RS tác động mức 1 b) RS tác động mức 0 Hình 5.8: Kí hiệu các RS - FF không đồng bộ 2.2 RS - FF đồng bộ Mạch RSFF đồng bộ hoạt động cần có tín hiệu đồng bộ, nghĩa là cần có xung đồng hồ (xung kích Ck). ngỏ ra của FF phụ thuộc vào trạng thái ngỏ vào R-S đồng thời cần xác định tại vị trí xung kích tác động Trong đó: Ck là tín hiệu điều khiển đồng bộ hay tín hiệu đồng hồ(Clock). Khảo sát hoạt động của mạch: S R Ck 1 2 3 4 s R Q Q a) Sơ đồ logic RS – FF đồng bộ b) ký hiệu RS – FF đồng bộ mức cao Hình 5.9: RSFF đồng bộ. Từ sơ đồ mạch RS – FF ta có bảng trạng thái ứng với xung kích Ck nhƣ sau Bảng 5.3: Bảng trạng thái RS – FF đồng bộ mức cao S R Ck Q X X 0 Q0 0 0 1 Q0 0 1 1 0 1 0 1 1 1 1 1 X Khoa KT Điện - Điện tử Trang 86 Giáo trình Vi mạch số Năm 2012 -Ck=0:Cổng NAND 3 và 4 khóa không cho dữ liệu đƣa vào.Vì cổng NAND 3 và 4 đều có ít nhất 1 ngõ vào Ck=0 1S R Q=Q0:RSFF giữ nguyên trạng thái cũ. -Ck=1:Cổng NAND 3 và 4 mở. Ngõ ra Q sẽ thay đổi tùy thuộc vào trạng thái của S và R. +S=0,R=0 1, 1S R Q=Q 0 +S=0,R=1 1, 0S R Q=0 +S=1,R=0 0, 1S R Q=1 +S=1,R=1 0, 0S R Q=X Trong trƣờng hợp này tín hiệu đồng bộ Ck tác động mức 1.Trong trƣờng hợp Ck tác động mức 0 thì ta mắc thêm cổng đảo nhƣ sau: R Ck S 1 2 3 4 S R Q Q S Ck R Q Q Hình 5.10:Mắc thêm cổng đảo trong trƣờng hợp Ck tác động mức 0. FF – RS đồng bộ còn có loại tác động bằng xung kích cạnh lên hay cạnh xuống, đây là loại đƣợc sử dụng phổ biến nhất Q Q SET CLR S R Q Q SET CLR S R Xung CK tác động cạnh lên Xung Ck tác động cạnh xuống Hình 5.11: RS – FF tác động bằng cạnh Khoa KT Điện - Điện tử Trang 87 Giáo trình Vi mạch số Năm 2012 a) RSFF kích bằng mức b) Bảng hàm kích RSFF Bảng 5.4: Bảng trạng thái và hàm kích RS –FF đồng bộ cổng NOR Ví dụ 1: Thiết kế mạch đếm đồng bộ - đếm xuống – xung Ck tác động cạnh lên, mod =12. Sử dụng FF RS Bảng trạng thái : Tp 0 0 0 0 0 0X 0X 0X 10 1 0 0 0 1 0X 0X 10 01 2 0 0 1 0 0X 0X X0 10 3 0 0 1 1 0X 10 01 01 4 0 1 0 0 0X X0 0X 10 5 0 1 0 1 0X X0 10 01 6 0 1 1 0 0X X0 X0 10 7 0 1 1 1 10 01 01 01 8 1 0 0 0 X0 0X 0X 10 9 1 0 0 1 X0 0X 10 01 10 1 0 1 0 X0 0X X0 10 11 1 0 1 1 01 0X 01 01 QDQC QBQA 00 01 11 10 00 0X 0X XX X0 01 0X 0X XX X0 N N+1 N Q Q SR 0 0 0X 0 1 10 1 0 01 1 1 X0 CK S R Q 0 X X ↑ 0 0 ↑ 0 1 0 1 ↑ 1 0 1 0 ↑ 1 1 Trạng thái cấm SDRD = Khoa KT Điện - Điện tử Trang 88 Giáo trình Vi mạch số Năm 2012 11 0X 10 XX 01 10 0X X0 XX X0 SD = QCQBQA RD = QDQBQA SC = 1 RC =QD SB= 1 RB = QB SA = A RA = QA Ví dụ 2: Vẽ dạng sóng ngỏ ra RS – FF đồng bộ mức cao 3.FLIP-FLOP JK 3.1 Cấu trúc: QDQC QBQA 00 01 11 10 00 0X 0X XX 0X 01 10 10 XX 0X 11 01 01 XX 0X 10 X0 X0 XX 0X QDQC QBQA 00 01 11 10 00 10 10 XX 10 01 01 01 XX 01 11 01 01 XX 01 10 10 10 XX 10 QDQC QBQA 00 01 11 10 00 0X X0 XX X0 01 0X X0 XX X0 11 10 01 XX 01 10 0X X0 XX X0 SCRC SBRB SARA Khoa KT Điện - Điện tử Trang 89 Giáo trình Vi mạch số Năm 2012 FF JK đƣợc tạo ra từ FF RS, nhằm khắc phục trạng thái cấm của RS – FF, nhờ tín hiệu hồi tiếp từ ngỏ ra thông qua cổng AND. Khi đó : J ~ S và K ~ R Q Q SET CLR S R J K Hình 5.12: Cấu trúc FF JK từ RS - FF 3.2 Kí hiệu và bảng trạng thái: JK – FF chỉ hoạt động ở chế độ đồng bộ J Q Q K SET CLR J Q Q K SET CLR J K Q Q CLK Tích cực mức cao J K Q Q CLK Tích cực mức thấp Hình 5.13: Ký hiệu các loại JK – FF CK J K Q 0 X X Q0 1 0 0 Q0 1 0 1 0 1 Xung CK tác động cạnh lên Xung CK tác động cạnh xuống Khoa KT Điện - Điện tử Trang 90 Giáo trình Vi mạch số Năm 2012 Bảng 5.5 : Bảng trạng thái JK – FF Bảng 5.6: Hàm kích JK – FF Theo bảng trạng thái ta thấy FF JK đã thoát khỏi trạng thái cấm và thay vào đó là trạng thái đảo ( khi J = K = 1 thì Q = 0 ) ngƣời ta lợi dụng trạng thái này để thiết kế mạch đếm. Ví dụ 1: Thiết kế mạch đếm đồng bộ đếm lên mod 5, xung Ck tác động cạnh lên . Ta có bảng trạng thái TP 0 0 0 0 0X 0X 1X 1 0 0 1 0X 1X X1 2 0 1 0 0X X0 1X 3 0 1 1 1X X1 X1 4 1 0 0 X1 0X 1X Gom nhóm: JC = QBQA KC = 1 JB = KB = Q JA = KA = 1 Ví dụ 2: Vẽ dạng sóng ngõ ra Q,tín hiệu vào J, K và xung CK tác động nhƣ hình vẽ? 1 1 0 1 0 1 1 1 Q0 N N+1 N Q Q JK 0 0 0X 0 1 1X 1 0 X1 1 1 X0 QC QBQA 0 1 00 0X X1 01 0X XX 11 0X XX 10 0X XX QC QBQA 0 1 00 0X 0X 01 1X XX 11 X1 XX 10 X0 XX QC QBQA 0 1 00 1X 0X 01 X1 XX 11 X1 XX 10 1X XX JCKC JAKA JBKB B Khoa KT Điện - Điện tử Trang 91 Giáo trình Vi mạch số Năm 2012 1 1 1 0 Ck J K Q Giải thích dạng tín hiệu ngõ ra -Giả sử ban đầu J=K=0,Q=1 thì Q0=1, -Khi cạnh lên thứ nhất của xung Ck xuất hiện,J=0,K=1,vì thế FF bị xóa vế trạng thái Q=0. -Khi cạnh lên thứ 2 của xung Ck xuất hiện J=K=1.Điều này làm cho FF bị lật so với trạng thái trƣớc đó tức là Q=1. -Khi cạnh lên thứ 3 của xung Ck xuất hiện J=K=0 nên FF không đổi trạng thái ở lần chuyển tiếp này tức là Q=1 -Khi cạnh lên thứ 4 xuất hiện,J=1,K=0.Đây là điều kiện thiết lập Q=1.Tuy nhiên trƣớc đó Q=1 nên vẫn duy trì ở trạng thái cũ. -Tới khi có cạnh lên của xung Ck kế tiếp xuất hiện J=1,K=1 điều này làm cho FF lật trạng thái từ trạng thái trƣớc đó Q=1 sang Q=0. 3.3 Ứng dụng của JK FF +Mạch chia tần số +Mạch đếm lên / xuống , đồng bộ hay không đồng bộ 3.4 Giới thiệu họ IC FF JK: IC 74LS112: gồm 2 FF – JK Khoa KT Điện - Điện tử Trang 92 Giáo trình Vi mạch số Năm 2012 a) Hình ảnh thật b) Sơ đồ chân Hình 5.14: Hình ảnh thực tế và sơ đồ chân IC 74LS112 IC 74LS73: Cũng gồm 2 FF – JK, Xung CK tác động cạnh xuống a) Hình ảnh thực tế b) Cấu trúc và sơ đồ chân Hình 5.15: Hình ảnh thực tế và sơ đồ chân IC 74LS73 4. FLIP-FLOP T 4.1 Cấu trúc: Từ JK-FF ngƣời ta nối chung các ngõ vào J,K tạo ngõ vào T nhƣ sau: T J K Ck FF Q Q Hình 5.16:Cấu trúc của FF-T CK T Q Khoa KT Điện - Điện tử Trang 93 Giáo trình Vi mạch số Năm 2012 4.2 Kí hiệu và bảng trạng thái FF-T T Ck FF Q Q Hình 5.17:Ký hiệu T - FF Bảng 5.7:Bảng trạng thái FF -T 4.3 Dạng sóng ngỏ ra Q (giản đồ thời gian) Ck T Q 0 0 0 1 Hình 5.18:Giản đồ thời gian ngỏ ra Q theo T Giải thích dạng sóng tín hiệu ngỏ ra: -Giả sử ban đầu T=0, Q=0. -Khi xuất hiện cạnh lên thứ nhất của xung Ck,T=0 nên FF vẫn giữ ở trạng thái Q=0. -Khi cạnh lên thứ 2 của xung Ck xuất hiện,T=1 nên FF lật trạng thái từ Q=0 sang Q=1. -Khi xuất hiện cạnh lên thứ 3 của xung Ck,T=0 nên FF vẫn giữ ở trạng thái Q=1 -Tại thời điểm cạnh lên kế tiếp của xung Ck xuất hiện,T=1 nên FF lại lật trạng thái từ Q=1 sang Q=0. -Khi cạnh lên kế tiếp của xung Ck xuất hiện,T=1 nên FF lại lật trạng thái từ Q=0 sang Q=1. FF T được sử dụng chính để tạo mạch đếm chia 2 5.FLIP-FLOP D và mạch ghi: 5.1 Cấu trúc : FF-D đƣợc xây dựng từ FF-JK hoặc FF-RS bằng cách thêm 1 cổng đảo 0 X Q0 0 Q0 1 0Q Khoa KT Điện - Điện tử Trang 94 Giáo trình Vi mạch số Năm 2012 D J K Ck Q Q D Ck Q Q S R Hình 5.19:FF-D đƣợc xây dựng từ FF-JK hoặc FF-RS Kí hiệu và bảng trạng thái FF-D D Ck Q Q FF Hình 5.20: Kí hiệu Bảng 5.8:Bảng trạng thái FF-D 5.2 Dạng sóng tín hiệu Q theo D ( giản đồ thời gian) C D Q 0 1 0 1 1 Hình 5.21:Dạng tín hiệu Q theo D Giải thích nguyên lý hoạt động: -Giả sử trạng thái ban đầu D=0,Q=1. -Khi xuất hiện cạnh lên lần thứ nhất của xung Ck,D=0 vì thế Q=0. -Khi xuất hiện cạnh lên lần thứ 2 của xung Ck,D=1 nên Q=1. -Khi xuất hiện cạnh lên lần thứ 3 của xung Ck,D=0 nên Q=1. -Tƣơng tự với các cạnh lên kế tiếp của xung Ck,các trạng thái ngõ vào ngõ ra nhƣ nhau ( D và Q cùng mức logic 0 hoặc 1). Ck D Q 0 0 1 1 Khoa KT Điện - Điện tử Trang 95 Giáo trình Vi mạch số Năm 2012 5.3 Mạch chốt giữ liệu D EN Q Q D EN Q Q SET CLR Hình 5.23:Ký hiệu và sơ đồ mạch chốt dữ liệu Giải thích nguyên lý hoạt động: -Khi EN = 1,D sinh ra mức 0 tại ngõ vào SET hay CLR ở mạch chốt NAND để làm cho Q đồng mức với D.Nếu D thay đổi trong khi EN=1,Q sẽ thay đổi y nhƣ vậy.Nói khác đi khi EN=1 thì Q và D cùng mức logic. -Khi EN=0 ngõ vào D bị cấm không ảnh hƣởng đến mạch chốt NAND vì ngã ra cả hai cổng NAND đều đƣợc giữ ở mức cao.Do đó Q và Q giữ nguyên trạng thái ban đầu.Nói cách khác,ngõ ra bị chốt ở mức đang có của nó và không thể thay đổi khi EN=0 bất chấp D thay đổi. 5.4 Giới thiệu họ IC FF-D: IC 74LS74: Hình 5.23:Sơ đồ mạch IC 7474 IC 74LS175: Khoa KT Điện - Điện tử Trang 96 Giáo trình Vi mạch số Năm 2012 a) Hình thực tế b) Sơ đồ chân Hình 5.24:Hình ảnh thực tế và sơ đồ chân IC 74LS175 MẠCH GHI DỊCH: Sơ đồ nguyên tắc và truyền 4 bit Hình 5.25: Sơ đồ mạch ghi dịch 4 bit - Là sơ đồ một mạch ghi dịch 4 bit đơn giản, mạch gồm 4 FF D nối thành chuỗi (ngõ ra Q của FF trƣớc nối vào ngõ vào D của FF sau) và các ngõ vào Ck đƣợc nối chung lại (các FF chịu tác động đổng thời). Mạch ghi dịch này có khả năng dịch phải. - Ngõ vào DA của FF đầu tiên đƣợc gọi là ngõ vào dữ liệu nối tiếp,các ngõ ra QA,QB,QC,QD, là các ngõ ra song song, ngõ ra của FF cuối cùng (FF D) là ngõ ra nối tiếp. - Trƣớc khi cho mạch hoạt động, tác dụng một xung xóa vào các ngõ vào (đƣa các chân đã đƣợc nối chung lên cao rồi xuống thấp) để các ngõ ra QA=QB=QC=QD =0. Khoa KT Điện - Điện tử Trang 97 Giáo trình Vi mạch số Năm 2012 - Cho dữ liệu vào DA,sau mỗi xung đồng hồ,dữ liệu từ trƣớc lần lƣợc truyền qua tầng sau. (giả sử DA là chuổi dữ liệu gồm 3 bit cao,2 bit thấp rồi 1 cao và 1 thấp), trạng thái các ngõ ra của các FF cho ở bảng sau: Vào Ra CL CK DA QA QB QC QD 0 X X 0 0 0 0 1 0 1 1 0 0 0 1 0 1 1 1 0 0 1 0 1 1 1 1 0 1 0 0 0 1 1 1 1 0 0 0 0 1 1 1 0 1 1 0 0 1 1 0 0 0 1 0 0 Bảng 5.9: Bảng trạng thái ghi dịch 4 Bit Ví dụ: IC 74164: dịch phải 8 bit. Gồm 8 D – FF IC hai hàng chân (14 chân), có chân Master Reset tích cực mức thấp. Ứng dụng làm thanh ghi dịch trong máy tính, dùng trong quảng cáo đèn quang báo. IC này thƣờng kết hợp với IC 555 để tạo xung dao động Ck ( Clock) và cần thêm khối khuếch đại dòng thƣờng dùng BJT để nâng dòng nhƣ C1815, A564. Khoa KT Điện - Điện tử Trang 98 Giáo trình Vi mạch số Năm 2012 Hình 5.25: Sơ đồ khối chức năng IC 74LS164 CP: Clock pulse, ngã vào xung đồng hồ tác động cạnh lên. MR: Master Reset, đây cũng là chân Clear của cả mạch, tác động thấp Ứng dụng của mạch ghi dịch: - Một số nhị phân khi dịch trái 1 bit, giá trị dƣợc nhân lên gấp đôi và đƣợc chia hai khi dịch phải một bit. Ví dụ nhƣ số 1010.00 = 1010 khi dịch trái thành 10100.0= 2010 và khi dịch phải thành 101.000 = 510 - Trong máy tính thanh ghi ( tên thƣờng gọi của mạch ghi dịch ) là nơi tạm trữ dữ liệu để thực hiện các phép tính, các lệnh cơ bản nhƣ quay, dịch - Ngoài ra, mạch ghi dịch còn những ứng dụng khác nhau nhƣ: tạo mạch đếm vòng, biến đổi dữ liệu nối tiếp song song, dùng thiết kế các mạch đèn trang trí , quảng cáo. Khoa KT Điện - Điện tử Trang 99 Giáo trình Vi mạch số Năm 2012 BÀI TẬP CHƢƠNG 5: Bài 1:Cho mạch logic nhƣ hình vẽ.Khảo sát dạng tín hiệu Y, Z, T theo tín hiệu A, B, C biết rằng giá trị ban đầu ngõ ra Q của chốt D và FLIP-FLOP D đều bằng 1. A B C Y T Z D Q D Q Q EN CK Q A B C Y Z T T= Z C Z C Bài 2: Vẽ giản đồ trạng thái của hệ tuần tự gồm 1 ngõ vào X và 2 T-FF nhƣ hình vẽ: Q1Qo X CK T Q CK Q T Q CK Q Từ sơ đồ ta có:T0=X+Q1 và T1= 1 0X Q Q Lập bảng chuyển trạng thái: Ta có giản đồ trạng thái: Q1Q0 00 01 10 11 X=0 1 1 0,1 0 0,1 Khoa KT Điện - Điện tử Trang 100 Giáo trình Vi mạch số Năm 2012 Bài 3: Vẽ dạng sóng và giải thích về các trạng thái ra tại Q của RSFF nhƣ hình dƣới. Biết Q0=0 và các ngõ vào S và R có dạng sóng bên dƣới S Q R Q S R Bài 4: Cho mạch điện nhƣ hình vẽ,vẽ dạng sóng ngõ ra QA, QB. Sau 6 xung Ck. J K Q Q J K Q Q QA QB QCk Bài 5: Giải thích nguyên lý hoạt động của mạch dùng 2 FF -JK Bài 6: Cho biết đây là mạch đếm mod mấy? hình thức đếm và vẽ dạng sóng ngỏ ra theo xung Ck.

File đính kèm:

giao_trinh_vi_mach_so_phan_1.pdf

giao_trinh_vi_mach_so_phan_1.pdf