Giáo trình Thí nghiệm điện tử

Nội Dung:

1. Máy OSC

2. Cấu tạo của OSCchức năng và cách sử dụng các bộ trên OSC

? POWER

- Power: Công tắc nguồn. Khi ở” ON” thì “ LED “sẽ sáng.

? INTENSITY CONTROL

- Intensity control: Dùng để thay đổi cường độ sáng của tia. Để tăng độ sáng ta vặn

theo chiều kim đồng hồ.

? FOCUS

- Điều chỉnh độ hội tụcủa tia (điều chỉnh độ sắc nét)

? TRIG LEVEL

- Trig leveldùng để điều chỉnh cho dạng sóng dứng yean và định điểm bắt đầu của

dạng sóng.

? TIDERRING COUPLING

- Dùng để lựa chọn kiểu lấy trigger (trigger mode).

- AUTO: Ở chức chức năng này, tín hiệu quét được phát ra khi không có tín hiệu

trigger thích hợp; tự động chuyển về quét trigger (trigger sweep) khi co tín hiệu

trigger thích hợp.

- NORM: Ở chức năng này, tín hiệu quet chỉ được phát khi có tín hiệu trigger thích

hợp.

- TV-V: dải tần trigger trong khoảng DC- 1KHz.

? TRIGGER SOUECE

- Dùng để lựa chọn nguồn lấy trigger.Bộ Thí Nghiệm Điện Tử Trang 4

- CH 1:Tín hiệu c ủa kênh SH1 trở thành nguồn trigger bất chấp vị trí nào của

VERTICAL MODE.

- CH 2: Tín hiệu của kênh SH2 trở thành nguồn trigger.

- LINE:Tín hiệu AC line dùng như nguồn lấy trigger

- EXT:Tín hiệu trigger được lấy từ đầu nối EXT TRIG.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Tóm tắt nội dung tài liệu: Giáo trình Thí nghiệm điện tử

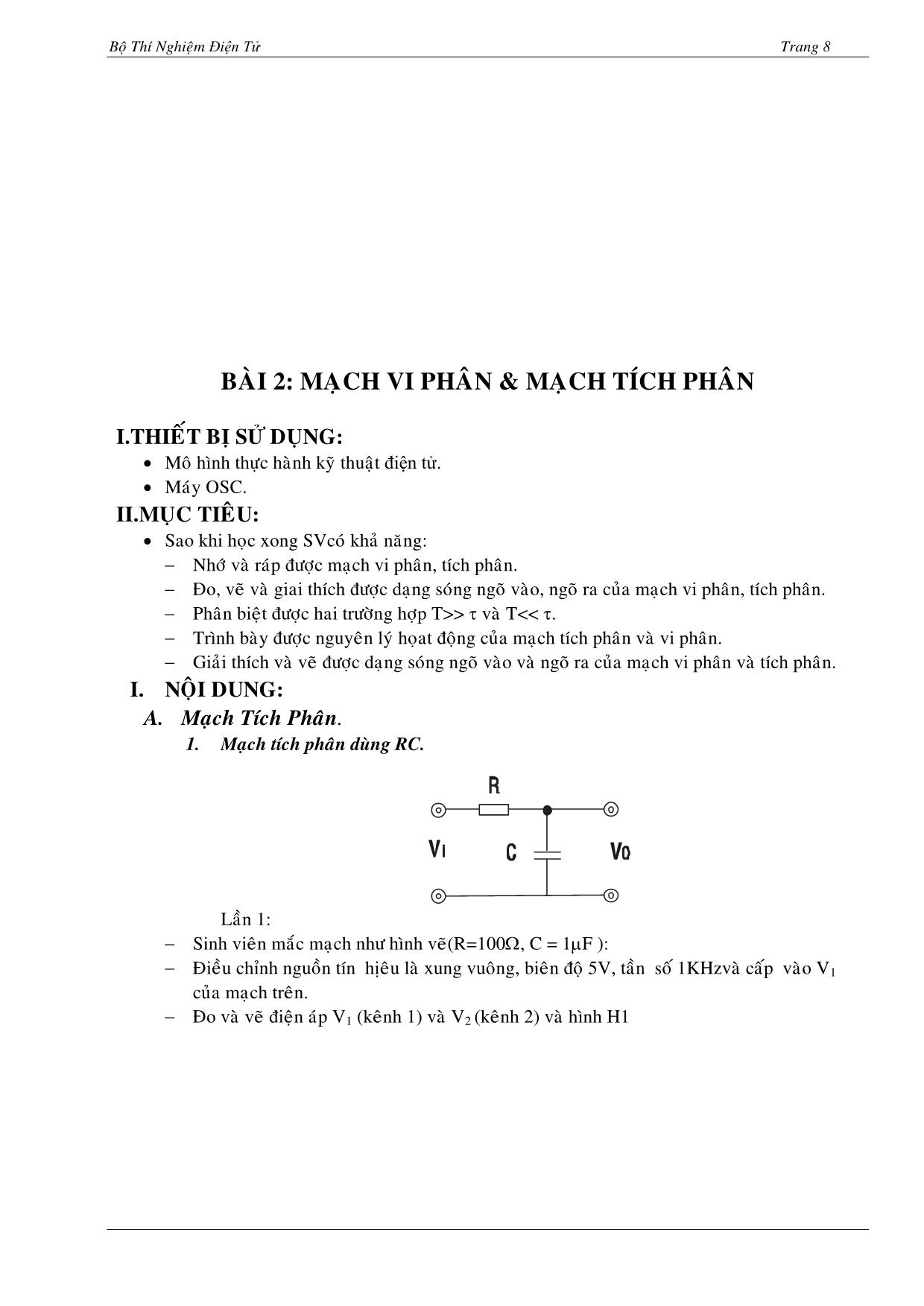

ỦY BAN NHÂN DÂN THÀNH PHỐ HỒ CHÍ MINH TRƯỜNG CAO ĐẲNG GIAO THƠNG VẬN TẢI KHOA KỸ THUẬT ĐIỆN – ĐIỆN TỬ ..o0o.. BÀI GIẢNG THÍ NGHIỆM ĐIỆN TỬ TP.HỒ CHÍ MINH, NĂM 2016 Bộ Thí Nghiệm Điện Tử Trang 1 THIẾT BỊ CHÍNH CHO CÁC BÀI THỰC TẬP I. Thiết Chính Bao Gồm Các Phần Chức Năng: 1.Nguồn Nuôi Dc (Dc Power Supply) +5VDC / 1A, - 5VDC / 0.5A , +12VDC / 1A , -12VDC / 1A có bảo vệ quá tải 2.Nguồn Dc Điều Chỉnh (Dc Adjust Power Supply) -Nguồn DC thay đổi liên tục được : 0V ... 25V / 1A, có bảo vệ quá tải 3. Nguồn Nuôi Ac (Ac Source) -Nguồn AC 6V, Ira max = 3A, có bảo vệ quá tải. 4. Máy Phát Chức Năng (Function Generator) -Dạng xung ra : vuông, tam giác và sin. -Tần số : 10 - 100 KHz, theo 5 khoảng và có điều chỉnh liên tục . -Độ chính xác 5% cho toàn thang. -Điện trở ra : 500 . -Thế ra : 16Vp-p (tải hở) ; 8Vp-p (với tải 50 ) 5. Khối đo dòng, áp: - Sử dụng các thang đo: A, µA, V, mV. - Hiển thị trên led 7 thanh. 6. Chỉ Thị Trạng Thái Logic ( Logic Indicators) : -4 LED chỉ thị trạng thái logic cao (1) và thấp (0). - Điện trở vào < 100 K. 7. Biến trở điều chỉnh: - 1K, 10K, 100K, 1M 8. Phụ Tùng : A. Dây nối. B. Cầu chì . C. Dây nguồn AC. II. Các Bài Thực Tập: STT Nội Dung Thiết Bị Vật Tư 1 Bài 1: Sử dụng máy OSC và mô hình THKT Điện Tử I. Máy OSC: 1. Cấu trúc của OSC. 2. Chức năng và cách sử dụng các bộ phận trên OSC. II. II. Mô hình THKT Điện Tử: 1. Giới thiệu. 2. Cách sữ dụng III. Thực hành: 1. Xác định hình dạng, biên độ, tần số tín hiệu. 2. Chỉnh một nguồn sao cho có Mô hình thực hành kỹ thuật điện tử Máy OSC Bộ Thí Nghiệm Điện Tử Trang 2 hình dạng, biên độ theo yêu cầu. 2 Bài 2: Mạch tích phân và vi phân I.Mạch tích phân(INTEGRATOR) 1. Mạch tích phân dùng RC 2. Mạch tích phân dùng Op- Amp II.Mạch vi phân(DIFFERENTIATOR) 1. Mạch vi phân dùng RC 2. Mạch vi phân dùng Op- Amp Mô hình thực hành kỹ thuật điện tử Máy OSC 3 Bài 3: Mạch dao động I. Mạch dao động đa hài transitor 1.Mạch lưỡng ổn 2.Mạch đơn ổn 3.Mạch phi ổn II. Mạch dao động đa hài dung Op- Amp 1.Mạch lưỡng ổn 2.Mạch đơn ổn 3.Mạch phi ổn. Mô hình thực hành kỹ thuật điện tử Máy OSC 4 Bài 4: Máy Phát Chức Năng - Máy Phát UJT Và Ứng Dụng I. Mạch tao xung dùngUJT 1. Nguyên lý hoạt động 2. Dạng sóng ra 3. Ứng dụng II. Mạch tạo xung dùng 555 1.Mạch đơn ổn 2. Mạch bất ổn III. Sơ đồ hình thành xung trên vi mạch thời gian. IV. Mạch phát xung dùng cổng logic. V. Mạch phát xung kiểu dịch pha dùng cổng logic VI. Mạch phát xung dùng thạch anh. VII. Sơ đồ máy phát chức năng Mô hình thực hành kỹ thuật điện tử Máy OSC Bộ Thí Nghiệm Điện Tử Trang 3 5 Bài 4: Cổng logic và ứng dụng 1. Khảo sát các cổng Logic 2. Bộ phát xung trên cổng Logic 3. Bộ hình thành xung. 4. Bộ so sánh số. 5. Bộ Trigger 6. Bộ Multiplexer 7. Bộ Decoder Mô hình thực hành kỹ thuật điện tử số. Máy OSC BÀI 1: SỬ DỤNG OSC VÀ MÔ HÌNH THỰC HÀNH KỸ THUẬT ĐIỆN TỬ I. Thiết Bị Sử Dụng: Mô hình thực hành kỹ thuật xung Máy OSC II. Mục Tiêu: Sau khi học xong SV co khả năng: Sử dụng được mô hình kỹ thuật xung và máy hiện sóng. III. Nội Dung: 1. Máy OSC 2. Cấu tạo của OSCchức năng và cách sử dụng các bộ trên OSC POWER - Power: Công tắc nguồn. Khi ở” ON” thì “ LED “sẽ sáng. INTENSITY CONTROL - Intensity control: Dùng để thay đổi cường độ sáng của tia. Để tăng độ sáng ta vặn theo chiều kim đồng hồ. FOCUS - Điều chỉnh độ hội tụcủa tia (điều chỉnh độ sắc nét) TRIG LEVEL - Trig leveldùng để điều chỉnh cho dạng sóng dứng yean và định điểm bắt đầu của dạng sóng. TIDERRING COUPLING - Dùng để lựa chọn kiểu lấy trigger (trigger mode). - AUTO: Ở chức chức năng này, tín hiệu quét được phát ra khi không có tín hiệu trigger thích hợp; tự động chuyển về quét trigger (trigger sweep) khi co tín hiệu trigger thích hợp. - NORM: Ở chức năng này, tín hiệu quet chỉ được phát khi có tín hiệu trigger thích hợp. - TV-V: dải tần trigger trong khoảng DC- 1KHz. TRIGGER SOUECE - Dùng để lựa chọn nguồn lấy trigger. Bộ Thí Nghiệm Điện Tử Trang 4 - CH 1:Tín hiệu c ủa kênh SH1 trở thành nguồn trigger bất chấp vị trí nào của VERTICAL MODE. - CH 2: Tín hiệu của kênh SH2 trở thành nguồn trigger. - LINE:Tín hiệu AC line dùng như nguồn lấy trigger - EXT:Tín hiệu trigger được lấy từ đầu nối EXT TRIG. MAIN, MIX, AND DELAY POSITION (PULLx10) - Dùng để điều chỉnh vị trí của tia sá ... OS phải biết nguồn cấp cho IC +5V hay +12V; mức logic tích cực ở chân điều khiển là 0 hay 1; từ đó lấy các chức năng trên kit ở các terminal TTL, CMOS đúng và thích hợp. Khi tháo dây nối ra khỏi điểm thử, phải cầm giữ ở đầu dây. B. CỔNG LOGIC VÀ ỨNG DỤNG (SỬ DỤNG MODULE DTSN02-2) Bộ Thí Nghiệm Điện Tử Trang 41 3.1 MỤC ĐÍCH: - Qua bài thí nghiệm sẽ khảo sát được hoạt động của các cổng logic. - Ứng dụng cổng logic: bộ phát xung trên cổng logic, bộ hình thành xung, bộ so sánh, trigger, multiplexer, decoder. 3.2 QUY ĐỊNH CHUNG: - Sử dụng đúng nguồn điện quy định. - Để thực hiện được các bài thí nghiệm ta phải dùng dây 4mm để cắm vào các jack trên bo mạch (bao gồm nguồn và các điểm thử). - Kiểm tra lại mạch trước khi cấp nguồn. 3.3 NỘI DUNG CÁC BÀI THỰC HÀNH: A. THỰC HÀNH VỚI CỔÂNG LOGIC: 1. Cổng NOT - Lắp mạch như hình, tín hiệu X được nối với công tắc logic. Thay đổi trạng thái X nhờ công tắc, nối ngõ ra Y với led hiển thị để quan sát. Quan sát led và lập bảng trạng thái. 1 27404X Y 2. Cổng AND a. Cổng AND 2 ngõ vào 1 2 3 7408 A Y B - Lắp mạch như hình, các tín hiệu A và B được nối với công tắc logic. Thay đổi trạng thái A, B nhờ các công tắc, nối ngõ ra Y với led hiển thị để quan sát. Quan sát led và điền vào bảng trạng thái. A B Y Y 0 0 0 1 1 0 1 1 b. Cổng AND 3 ngõ vào - Thực hiện cổng AND 3 ngõ vào từ 2 cổng AND 2 ngõ vào. Quan sát led và điền vào bảng trạng thái. 1 2 3 7408 A Y B 4 5 6 7408C Y 1 2 13 12 A B C A B C Y Y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Bộ Thí Nghiệm Điện Tử Trang 42 4 5 67400 B A Y B A Y 9 10 8 7432 3. Cổng NAND a. Cổng NAND 2 ngõ vào - Lắp mạch như hình vẽ, các tín hiệu A và B được nối với công tắc logic. Thay đổi trạng thái A, B nhờ các công tắc, nối ngõ ra Y với led hiển thị để quan sát. Lưu ý: led sáng khi Y ở trạng thái cao hay Y ở trạng thái thấp . Quan sát led và điền vào bảng trạng thái. b. Cổng NAND 3 ngõ vào - Thực hiện cổng NAND 3 ngõ vào từ 2 cổng NAND 2 ngõ vào. Quan sát led và điền vào bảng trạng thái. A Y B C Y A B C 1 2 37400 4 5 67400 1 2 13 12 A B C Y Y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 4. Cổng OR a. Cổng OR 2 ngõ vào - Lắp mạch như hình vẽ, các tín hiệu A và B được nối với công tắc logic. Thay đổi trạng thái A, B nhờ các công tắc, nối ngõ ra Y với led hiển thị để quan sát. Lưu ý: led sáng khi /Y ở trạng thái cao hay Y ở trạng thái thấp. Quan sát led và điền vào bảng trạng thái. A B Y Y 0 0 0 1 1 0 1 1 b. Cổng OR 3 ngõ vào - Tương tự các bài thí nghiệm ở trên, thực hiện cổng OR 3 ngõ vào. Quan sát led và điền vào bảng trạng thái. A B C Y Y A B Y Y 0 0 0 1 1 0 1 1 Bộ Thí Nghiệm Điện Tử Trang 43 B A Y 2 3 1 7402 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 5. Cổng NOR a. Cổng NOR 2 ngõ vào - Lắp mạch như hình vẽ, các tín hiệu A và B được nối với công tắc logic. Thay đổi trạng thái A, B nhờ các công tắc, nối ngõ ra Y với led hiển thị để quan sát. Lưu ý: led sáng khi /Y ở trạng thái cao hay Y ở trạng thái thấp. Quan sát led và điền vào bảng trạng thái. b. Cổng NOR 3 ngõ vào - Tương tự các bài thí nghiệm ở trên, thực hiện cổng OR 3 ngõ vào. Quan sát led và điền vào bảng trạng thái. A B C Y Y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 6. Ứng dụng NAND, NOR a. Tạo cổng NOT từ cổng NAND bằng 2 cách: - Ta sử dụng công thức để thực hiện cổng NOT từ cổng NAND. Y=A = A.A = A.1 Cách 1: Dùng chung tín hiệu ngõ vào Cách 2: Một chân tín hiệu ngõ vào luôn ở mức cao b. Tạo cổng NOT từ cổng NOR bằng 2 cách: - Ta sử dụng công thức để thực hiện cổng NOT từ cổng NOR. Y=A = A+A = A+0 Sinh viên tự thực hiện. c. Thực hiện hàm Boole bằng sơ đồ logic Cấu trúc AND-OR - Sơ đồ logic AND-OR được tạo ra từ hàm Boole dạng tổng các tích. A B Y Y 0 0 0 1 1 0 1 1 Bộ Thí Nghiệm Điện Tử Trang 44 - Ví dụ: Vẽ sơ đồ logic cho hàm sau: F(A,B,C,D) = A.B+B.C.D 9 10 8 7408 B A Y 2 3 1 7402 1 2 13 12 B C D Hướng dẫn: Sinh viên kết nối theo sơ đồ trên. Lưu ý: Cổng AND 3 ngõ vào được tạo như bài thí nghiệm 2.2. Cấu trúc OR-AND - Sơ đồ logic OR-AND được tạo ra từ hàm Boole dạng tích các tổng.. - Ví dụ: Vẽ sơ đồ logic cho hàm sau: - F(A,B,C,D) = (B+C).(A+C+D) - Sinh viên tự kết nối mạch. Lưu ý: Công OR 3 ngõ vào được thực hiện như bài thí nghiệm ở mục 4.2 Cấu trúc NAND-NAND - Sơ đồ logic NAND-NAND được tạo ra từ hàm Boole dạng tổng các tích sau đó lấy bù hai lần và áp dụng định lý De Morgan. Ví dụ: Vẽ sơ đồ logic cho hàm sau: F(A,B,C,D)=A.B+B.C.D =A.B+B.C.D =A.B.B.C.D Y 1 2 37400 1 2 13 12 1 2 37400 B B A D C Cấu trúc NOR-NOR - Sơ đồ logic NOR-NOR được tạo ra từ hàm Boole dạng tích các tổng, sau đó lấy bù hai lần và áp dụng định lý De Morgan. - Ví dụ: Vẽ sơ đồ logic cho hàm sau: F(A,B,C,D) = (B+C).(A+C+D) = (B+C).(A+C+D) = (B+C)+(A+C+D) Bộ Thí Nghiệm Điện Tử Trang 45 - Sinh viên tự kết nối mạch. Lưu ý: Cổâng NOR 3 ngõ vào được thực hiện như bài thí nghiệm ở mục 5.2 B. TỔ HỢP MẠCH LOGIC: 1. Tổ hợp cổng logic - Sinh viên dùng các cổng logic để thực hiện các hàm sau: a) Hàm logic của EXOR: F(A,B) = A.B+A.B - Hướng dẫn: Sơ đồ kết nối như sau: Y 1 2 3 7432 1 27404 1 27404 1 2 37400 4 5 67400 A B b) Hàm logic của EXNOR: F(A,B) = A.B+A.B - Sinh viên thực hiện tương tự phần thí nghiệm trên. 2. Đơn giản mạch logic - Rút gọn hàm sau F(A,B,C,D) = (0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14) - Bảng chân trị như sau: TT A B C D F 0 0 0 0 0 1 1 0 0 0 1 1 2 0 0 1 0 1 3 0 0 1 1 0 4 0 1 0 0 1 5 0 1 0 1 1 6 0 1 1 0 1 7 0 1 1 1 0 8 1 0 0 0 1 9 1 0 0 1 1 10 1 0 1 0 0 11 1 0 1 1 0 12 1 1 0 0 1 13 1 1 0 1 1 14 1 1 1 0 1 15 1 1 1 1 0 - Hướng dẫn: Dùng bìa Karnaugh để rút gọn hàm. Hàm rút gọn có dạng như sau: F(A,B,C,D)=C+A.D+B.D AB CD 00 01 11 10 Bộ Thí Nghiệm Điện Tử Trang 46 00 01 11 10 F(A,B,C,D) = - Dựa vào hàm rút gọn, sinh viên tự kết nối mạch và kiểm chứng bảng chân trị. C. ỨNG DỤNG CỔNG LOGIC: 1. Bộ phát xung trên cổng logic: - Mắc mạch như hình vẽ: 1 2 7414 3 4 7414 5 6 7414 9 8 7414100k C4 474 500K 47K Y - Cấp nguồn cho module 3. - Nối ngõ ra Y với led hiển thi trạng thái - Vặn biến trở VR và quan sát led trạng thái. - Thay tụ và rút ra nhận xét. ........................................................................................................................................................ ........................................................................................................................................................ ........................................................................................................................................................ ........................................................................................................................................................ ........................................................................................................................................................ ........................................................................................................................................................ ........................................................................................................................................................ ........................................................................................................................................................ 2. Bộ hình thành xung: - Mắc mạch như hình vẽ: - Cấp nguồn cho module 3. - Nối ngõ ra Y với led hiển thi trạng thái - Bật/tắt công tắc và quan sát led trạng thái. - Rút ra nhận xét. . . . . . . . . 3. Bộ so sánh số: - Mắc mạch như hình vẽ: Bộ Thí Nghiệm Điện Tử Trang 47 - Cấp nguồn cho module 3. - Dùng 2 DataSW nối vào 2 điểm A,B. - Nối ngõ ra Y1,Y2,Y3 với 3 led hiển thi trạng thái - Bật/tắt công tắc SW và quan sát led trạng thái. - Lập bảng trạng thái và rút ra nhận xét. INPUTS OUTPUTS A B Y1 Y2 Y3 L L H L L H H H 4. Bộ Trigger: a) Trigger RS - Sơ đồ logic, ký hiệu logic và bảng chân lý của trigger RS xây dựng từ cửa không hoặc. S R Q Q 0 0 Không đổi 0 1 0 1 1 0 1 0 1 1 Không xác định - Nếu R và S đều bằng 0, mạch hoạt động như một yếu tố hai trạng thái cân bằng. Do tính chất phản hồi khép kín mà đầu ra Q = 0 hay Q = 1. Giá trị 0 hay 1 hoàn toàn là ngẫu nhiên. - Từ sơ đồ logic ta dễ dàng thấy rằng chỉ cần thay đổi mức logic đầu vào S hoặc R, trigger sẽ “chọn” một trạng thái cân bằng. Nếu S = 1, R = 0 thì đầu ra Q = 1 ; Đầu vào S là đầu “xác lập” (Set hay Preset, có nghĩa là xác lập). Nếu S = 0. R = 1 thì đầu ra Q = 0 ; Đầu vào R là đầu “xoá” (Reset hay Clear, có nghĩa là xoá). - Giản đồ thời gian của trigger RS như hình vẽ dưới đây với đường chấm chấm chỉ nguyên nhân của sự thay đổi trạng thái. Bộ Thí Nghiệm Điện Tử Trang 48 Trigger SR - Trigger RS nói trên thuộc loại tác động cao. Có thể xây dựng trigger SR có tác động thấp từ hai cửa NOT vàAND. - Trigger RS (hay RS) rất nhạy với tác động của đầu vào R và S và được gọi là trigger không đồng bộ. Tuy nhiên, nếu cải biến đi một chút bằng cách thêm một đầu vào cho phép (Enable) hay đầu vào xung nhịp (Clock) sao cho chỉ khi nào có tác động của đầu vào này thì trigger mới chuyển trạng thái theo tác động của S hay R. Trigger loại này gọi là Trigger RST. - RST là Trigger có đồng bộ. b) Trigger D: - Trong kỹ thuật vi tính, ta cần lưu trữ thông tin, mỗi bit thông tin được thể hiện trên một đường tín hiệu. Trigger D có thể được dùng để lưu trữ bit thông tin này. Hình sau đây là sơ đồ logic, ký hiệu logic và bảng chân lý của trigger D. Điều đặc biệt quan trọng trong sơ đồ này là nhờ cửa đảo mà đầu vào S và R luôn luôn ở hai trạng thái trái ngược nhau. S R Q Q 0 0 Không đổi 0 1 0 1 1 0 1 0 1 1 Không xác định Bộ Thí Nghiệm Điện Tử Trang 49 S CK Q Q x 0 Không đổi 0 1 0 1 1 1 1 0 - Giản đồ thời gian sau mô tả sự đúng đắn của bảng chân lý. Khi C K = 1 thì lối ra Q “theo đúng” số liệu thông tin D nghĩa là lối ra Q là sự trễ của lối vào D một ọt rất nhỏ. Khi C K = 0 thì lối ra Q không thay đổi. 5. Bộ MULTIPLEXER: - Bộ Multiplexer 4 ->1 được xây dựng từ cổng AND 3 ngõ vào, OR 2 ngõ vào và cổng NOT. Để điều khiển chọn 1 trong 4 kênh vào đòi hỏi tín hiệu điều khiển phải 2 bit: X= X- oX1. Lập bảng giá trị 5.1, trong đó nếu 10 XX = 00 ngõ ra Y nối với kênh Ao, khi 10 XX = 01, Y nối với kênh A1, khi 10 XX = 10, Y nối với kênh A2 và khi 10 XX =11, Y nối với kênh A3. Từ bảng giá trị 5.1 suy ra biểu thức ngõ ra của mạch như sau: .... 103102101100 XXAXXAXXAXXAY - Bảng 5.1: - Sơ đồ kết nối mạch: Xo X1 Y 0 0 Ao 0 1 A1 1 0 A2 1 1 A3 Bộ Thí Nghiệm Điện Tử Trang 50 1 2 13 1274LS15 3 4 5 674LS15 1 2 13 12 74LS15 9 10 11 8 74LS15 13 12 11 10 A Y2 Y1 Y0 X1 X0 Y3 A0 A1 A2 A3 X0 X1 Y 1 2 13 12 74LS15 9 10 11 8 74LS15 9 10 11 8 74LS15 1 2 13 12 74LS15 11 10 7405 13 12 7405 1 2 3 74LS32 4 5 6 74LS32 9 10 8 74LS32 X0 X1 Y 0 0 0 1 1 0 1 1 - Nối các ngõ vào A0, A1, A2, A3, X0, X1 với các Data SW trên module nguồn. - Nối ngõ ra Y với Led hiển thị trạng thái trên module nguồn. - Thay đổi các Data SW để thay đổi ngõ ra Y. - Thay đổi các giá trị logic các lối vào theo bảng chân lý thông qua các Data SW, quan sát giá trị logic lối ra Y và điền đầy đủ vào bảng chân lý- So sánh với bảng chân lý ở phần lý thuyết . 6. Bộ DECODER - Để xây dựng mạch phân kênh với 4 đường tín hiệu ra ta sử dụng cổng AND 3 ngõ vào,và cổng NOT. - Để điều khiển 4 đường ra đòi hỏi tín hiệu điều khiển 2 bit: X=xox1. - Lập bảng giá trị của mạch (bảng 6.1). - Trong đó: 10 XX = 00 A nối với Y0. 10 XX = 01 A nối với Y1. 10 XX = 10 A nối với Y2. 10 XX =11 A nối với Y3. - Bảng 6.1: - Từ bảng 6.1 chúng ta viết các biểu thức ngõ ra. Y0=A. 10 XX Y1=A. 10 XX Y2=A. 10 XX Y3=A. 10 XX Vào Ra X1 X0 Y0 Y1 Y2 Y3 0 0 A 0 0 0 0 1 0 A 0 0 1 0 0 0 A 0 1 1 0 0 0 A Bộ Thí Nghiệm Điện Tử Trang 51 - Sơ đồ mạch: Vào Ra X1 X0 Y0 Y1 Y2 Y3 0 0 0 1 1 0 1 1 - Nối các ngõ vào A, X0, X1 với các Data SW trên module nguồn. - Nối ngõ ra Y0, Y1, Y2, Y3 với Led hiển thị trạng thái trên module nguồn. - Thay đổi các Data SW để thay đổi các ngõ ra Y0, Y1, Y2, Y3. - Thay đổi các giá trị logic các lối vào theo bảng chân lý thông qua các Data SW, - Quan sát giá trị logic lối ra Y0, Y1, Y2, Y3 và điền đầy đủ vào bảng chân lý - So sánh với bảng chân lý ở phần lý thuyết . .............................................................................................................................. .............................................................................................................................. .............................................................................................................................. .............................................................................................................................. .............................................................................................................................. .............................................................................................................................. ..............................................................................................................................

File đính kèm:

giao_trinh_thi_nghiem_dien_tu.pdf

giao_trinh_thi_nghiem_dien_tu.pdf