Thiết kế bộ xáo trộn cho hệ thống BICM-ID truyền dẫn qua kênh pha đinh

Ảnh hưởng của kênh pha đinh lên chất lượng hệ thống truyền tin vô tuyến là “lỗi cụm”.

Hệ thống điều chế mã có xáo trộn bit và giải mã lặp sử dụng bộ xáo trộn bít để phân tán

“lỗi cụm” thành các lỗi đơn giúp cho quá trình giải mã trở nên đáng tin cậy hơn. Ngoài ra,

bộ xáo trộn trong hệ thống BICM-ID có tác dụng làm tăng khoảng cách Hamming tối

thiểu giữa các chuỗi bit mã, do đó, hạn chế sự lan truyền lỗi của quá trình giải mã lặp. Như

vậy, thiết kế bộ xáo trộn bít là một trong những yếu tố quyết định chất lượng của hệ thống

BICM-ID. Những bộ xáo trộn bít sử dụng trong BICM-ID được giới thiệu trong các tài

liệu [4, 8, 10] có hiệu quả cao nhưng thuật toán phức tạp và triển khai phần cứng thực tế

khó. Trong bài báo này, chúng tôi nghiên cứu về các bộ xáo trộn cơ bản, từ đó, đề xuất

một bộ xáo trộn mới có hiệu suất tốt và dễ triển khai trong thực tế.

Phần hai của bài báo trình bày mô hình hệ thống BICM-ID, trong phần ba trình bày

khái quát các bộ xáo trộn cơ bản và đề xuất bộ xáo trộn bít mới. Phần bốn và phần năm

trình bày kết quả mô phỏng kết luận của bài báo.

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tóm tắt nội dung tài liệu: Thiết kế bộ xáo trộn cho hệ thống BICM-ID truyền dẫn qua kênh pha đinh

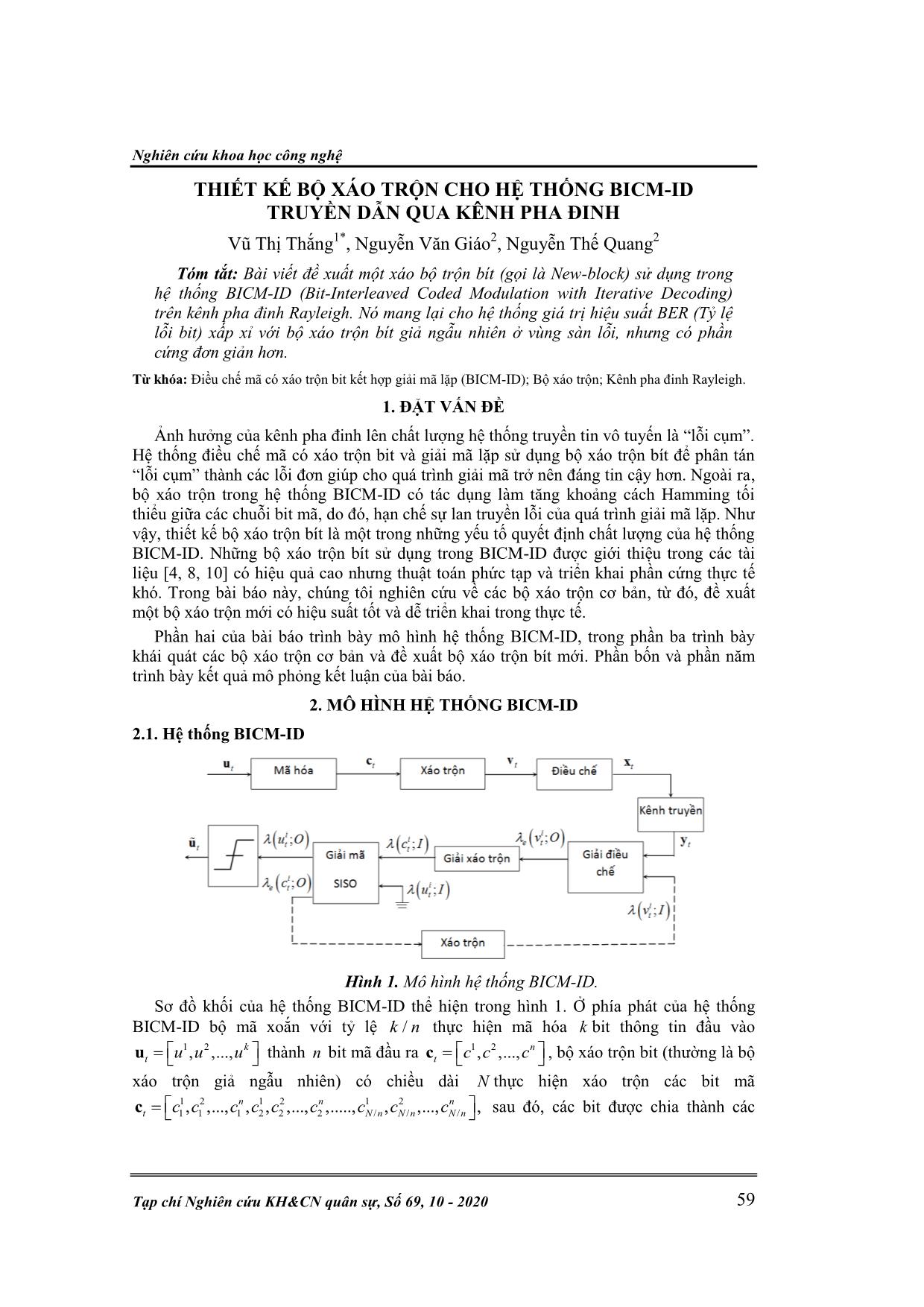

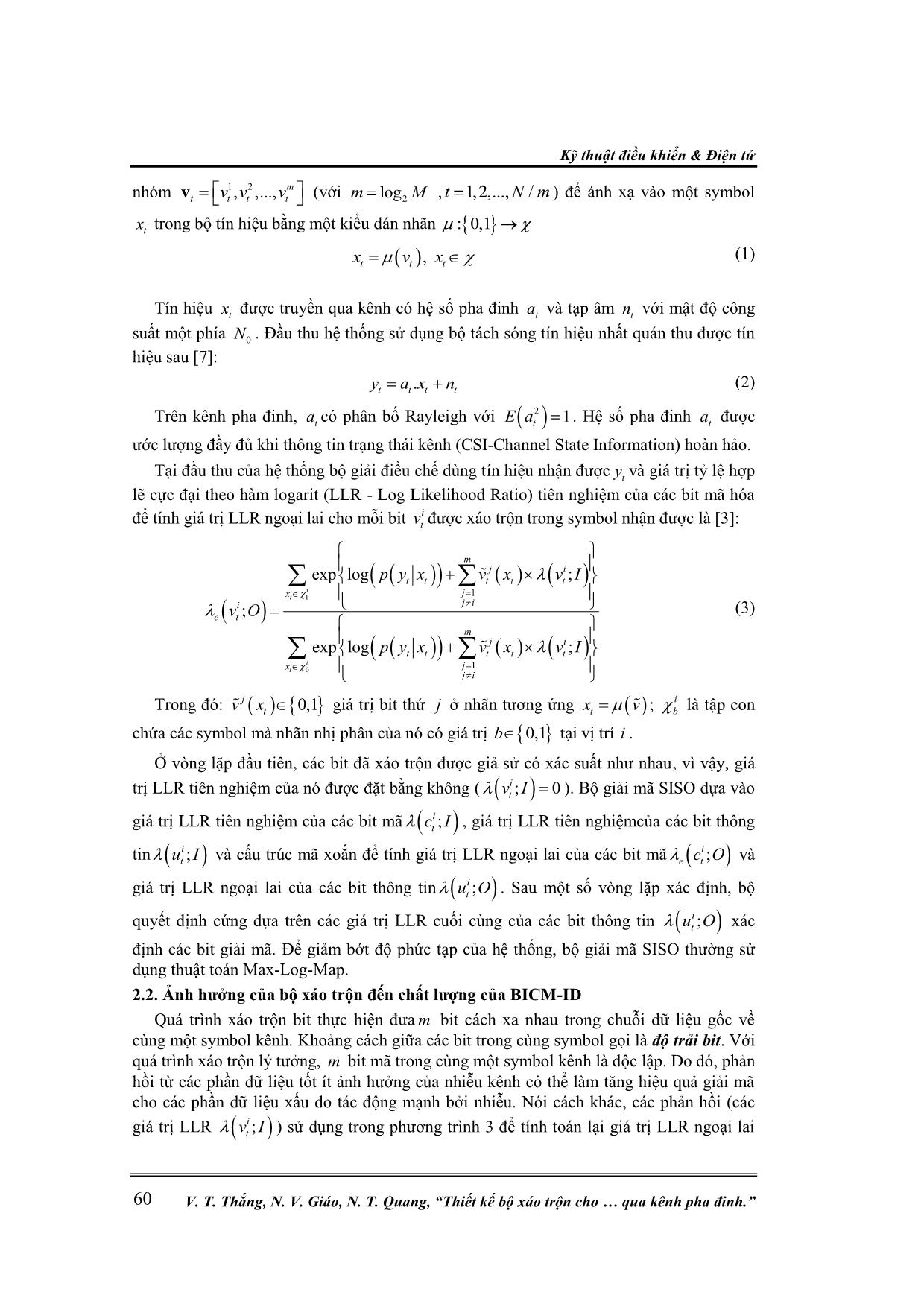

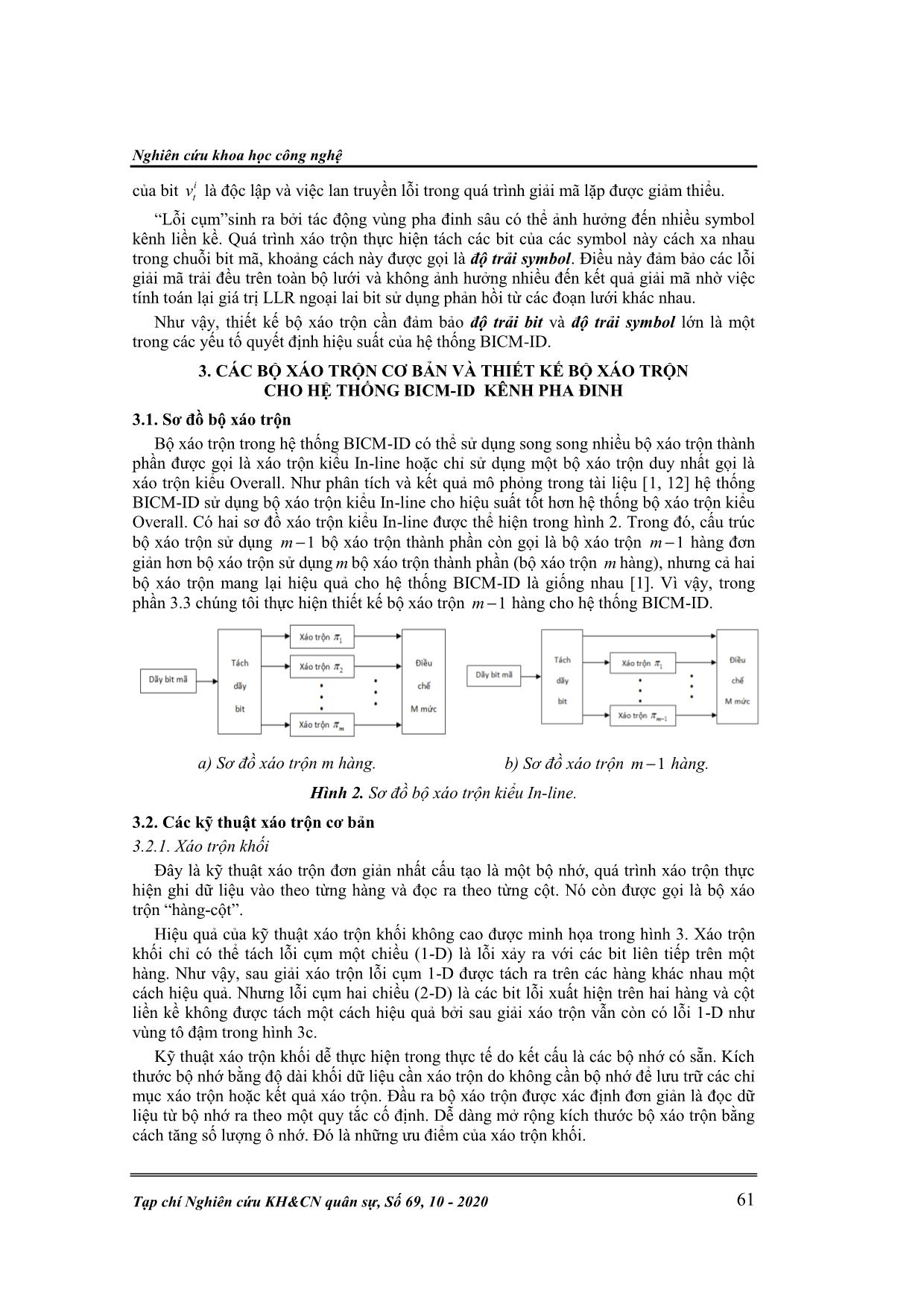

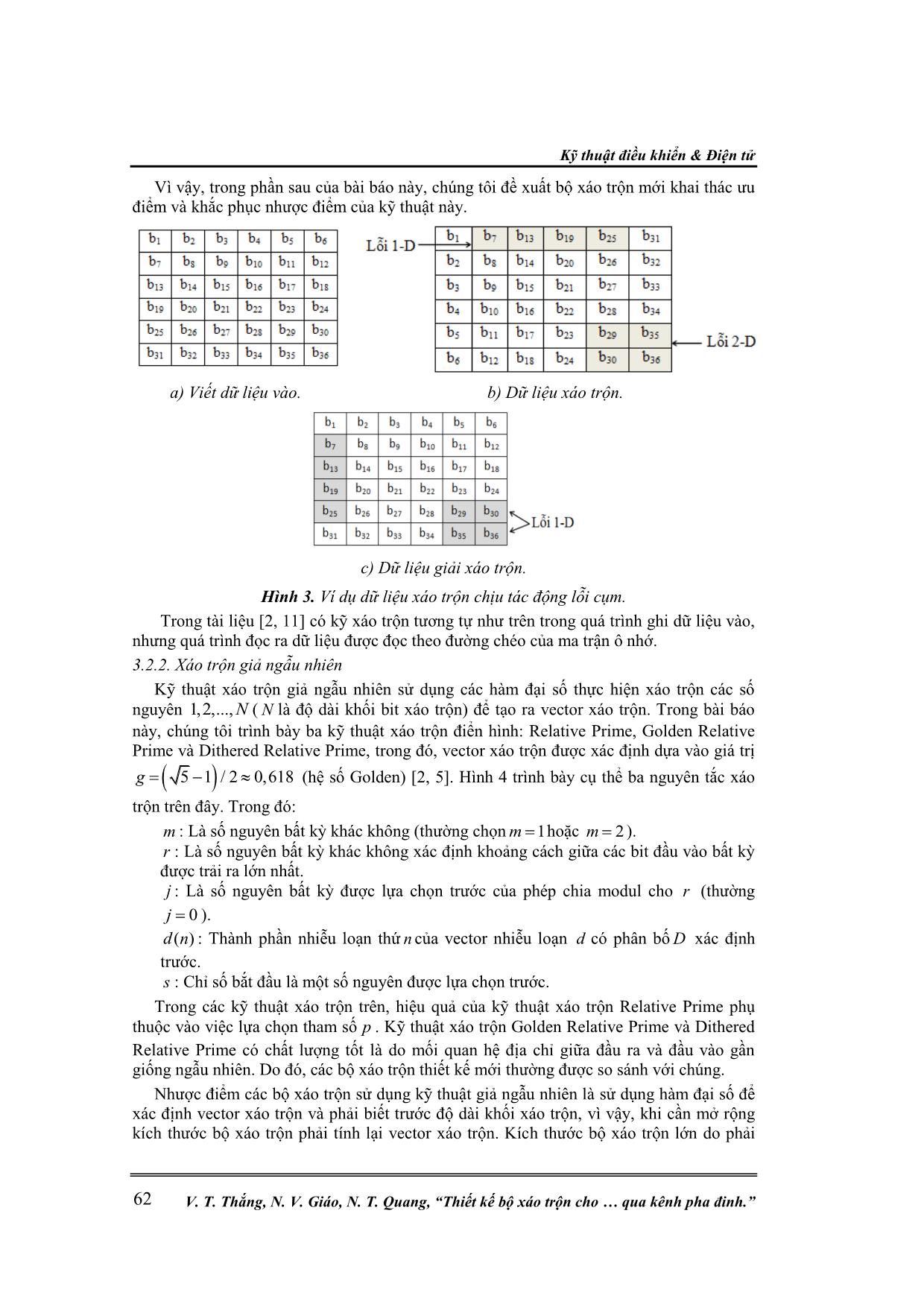

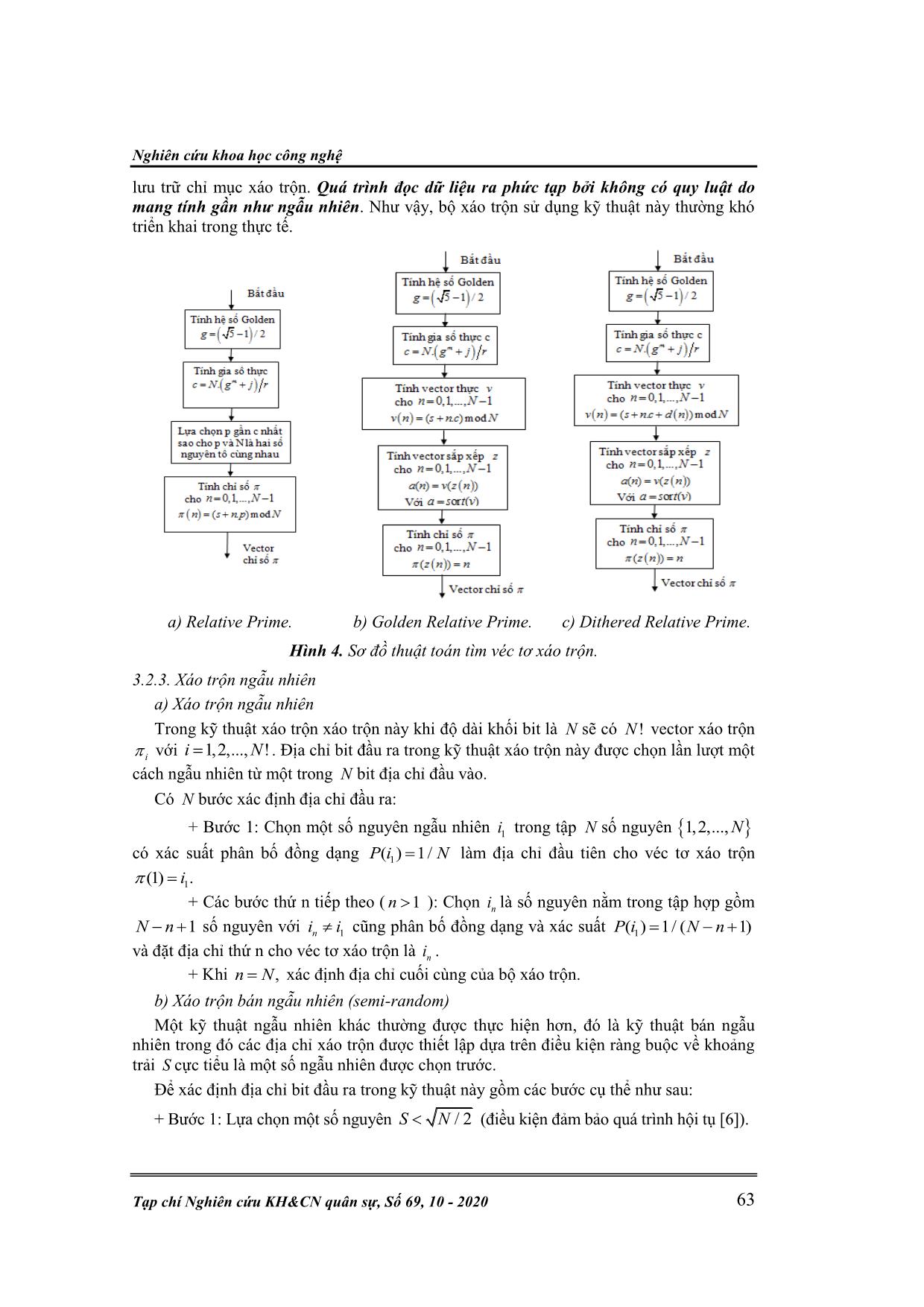

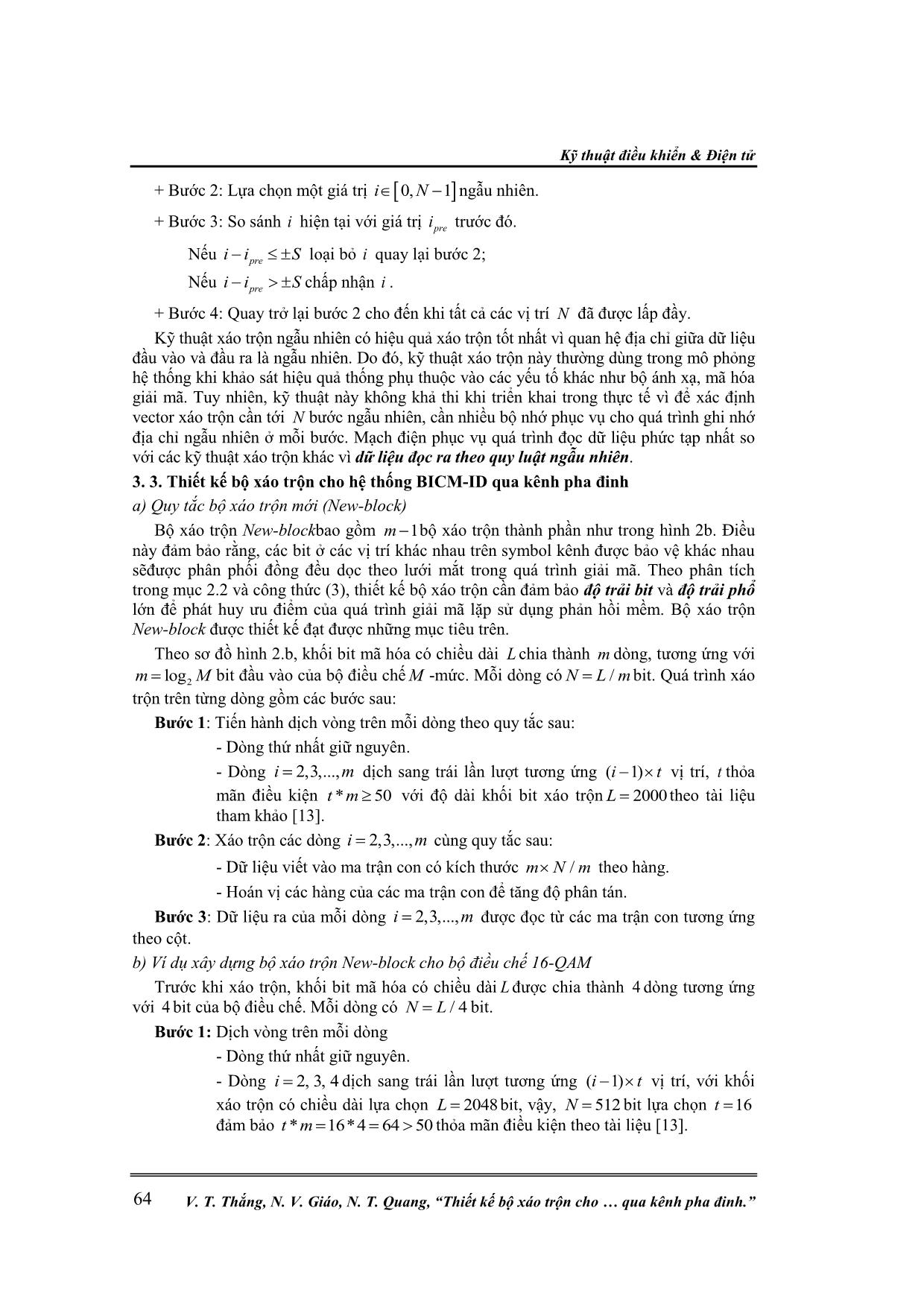

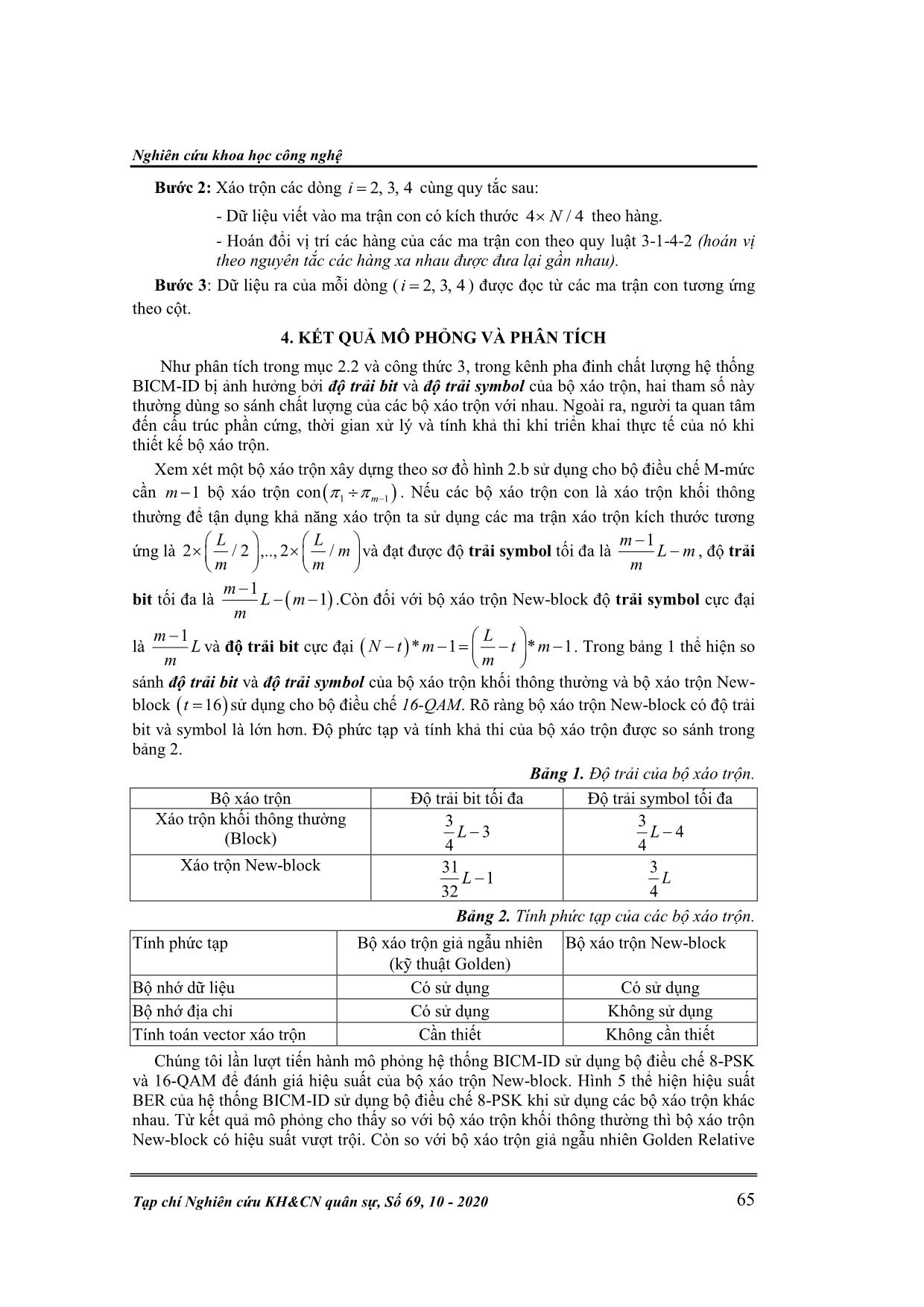

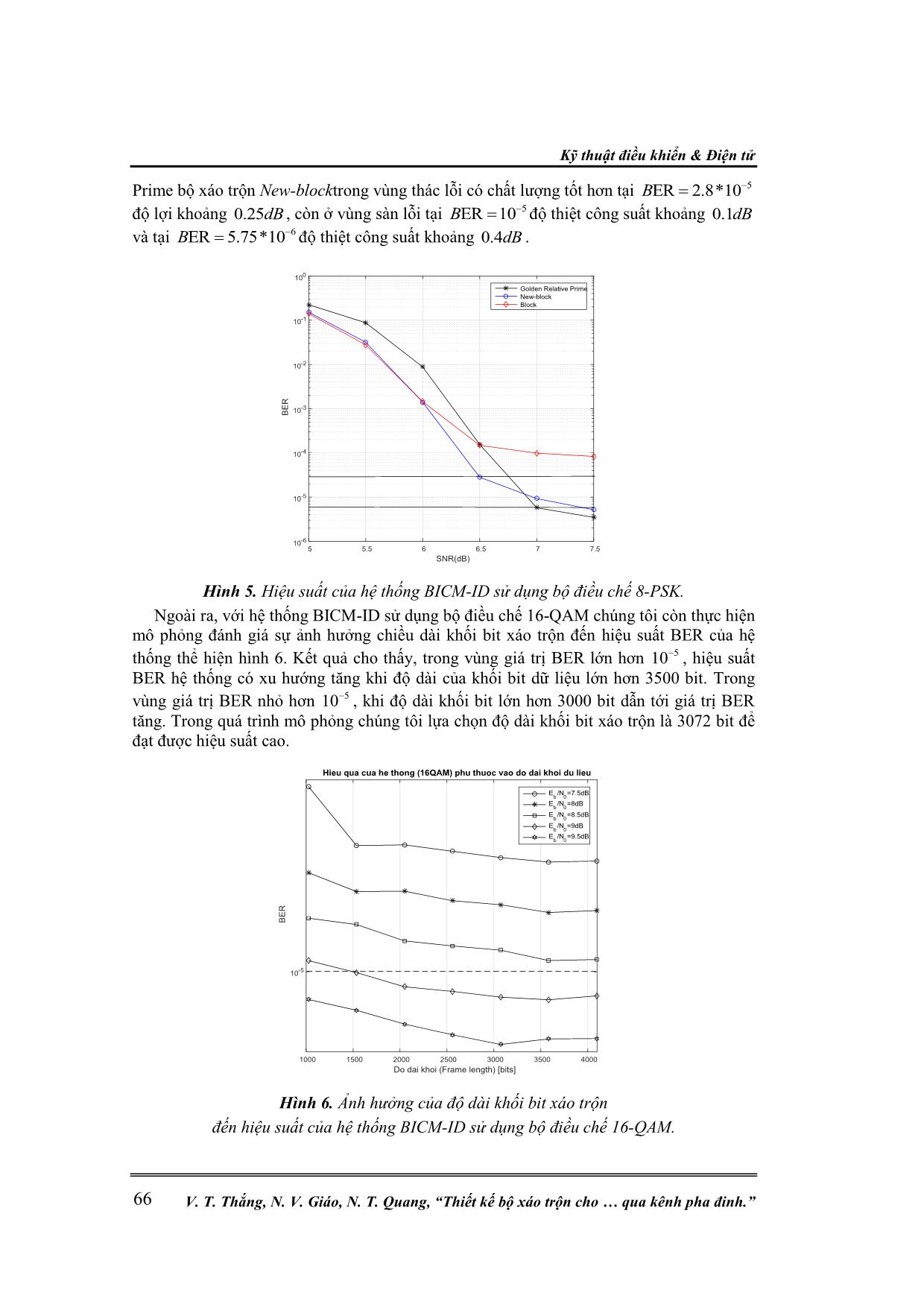

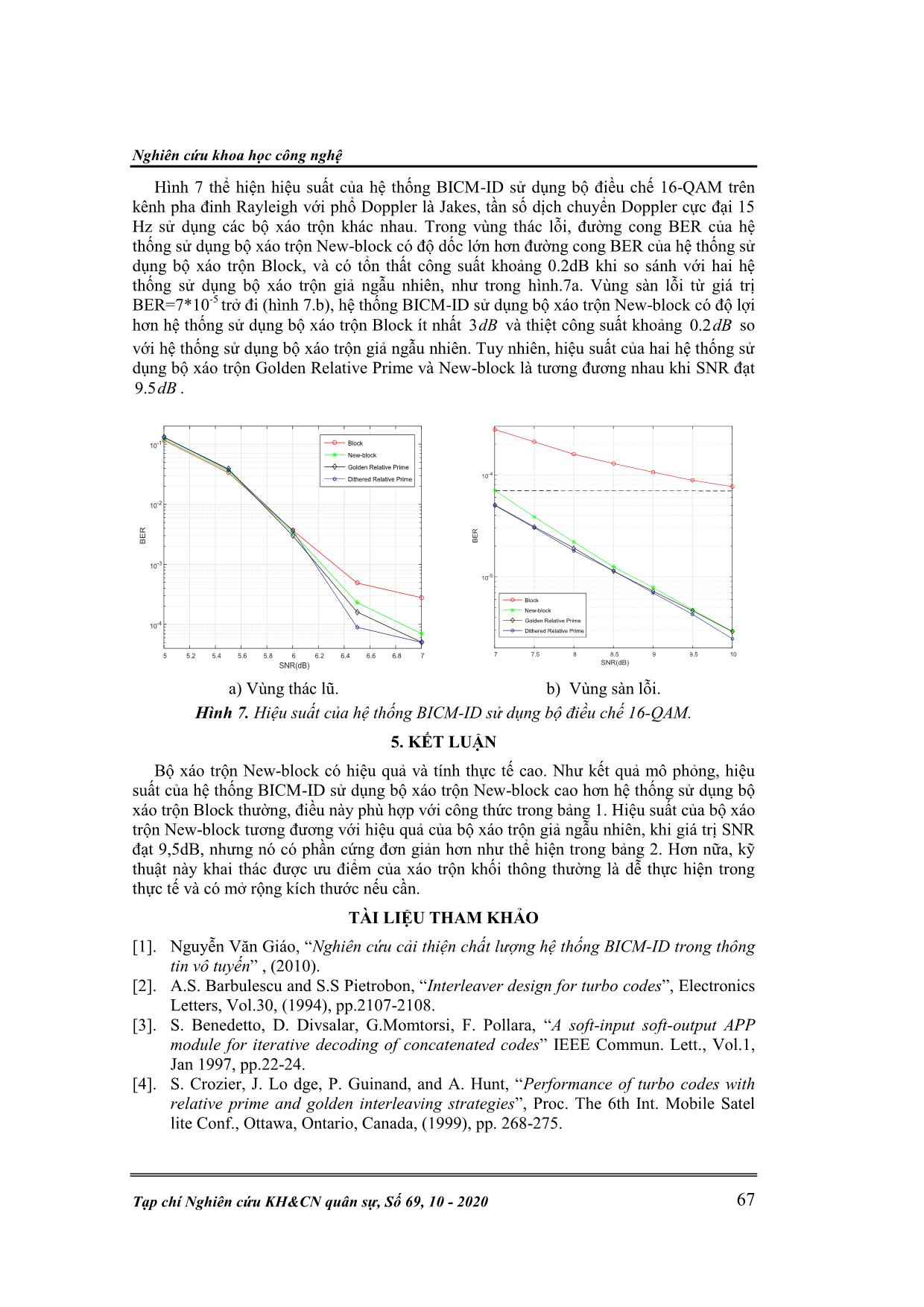

Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 69, 10 - 2020 59 THIẾT KẾ BỘ XÁO TRỘN CHO HỆ THỐNG BICM-ID TRUYỀN DẪN QUA KÊNH PHA ĐINH Vũ Thị Thắng1*, Nguyễn Văn Giáo2, Nguyễn Thế Quang2 Tóm tắt: Bài viết đề xuất một xáo bộ trộn bít (gọi là New-block) sử dụng trong hệ thống BICM-ID (Bit-Interleaved Coded Modulation with Iterative Decoding) trên kênh pha đinh Rayleigh. Nó mang lại cho hệ thống giá trị hiệu suất BER (Tỷ lệ lỗi bit) xấp xỉ với bộ xáo trộn bít giả ngẫu nhiên ở vùng sàn lỗi, nhưng có phần cứng đơn giản hơn. Từ khóa: Điều chế mã có xáo trộn bit kết hợp giải mã lặp (BICM-ID); Bộ xáo trộn; Kênh pha đinh Rayleigh. 1. ĐẶT VẤN ĐỀ Ảnh hưởng của kênh pha đinh lên chất lượng hệ thống truyền tin vô tuyến là “lỗi cụm”. Hệ thống điều chế mã có xáo trộn bit và giải mã lặp sử dụng bộ xáo trộn bít để phân tán “lỗi cụm” thành các lỗi đơn giúp cho quá trình giải mã trở nên đáng tin cậy hơn. Ngoài ra, bộ xáo trộn trong hệ thống BICM-ID có tác dụng làm tăng khoảng cách Hamming tối thiểu giữa các chuỗi bit mã, do đó, hạn chế sự lan truyền lỗi của quá trình giải mã lặp. Như vậy, thiết kế bộ xáo trộn bít là một trong những yếu tố quyết định chất lượng của hệ thống BICM-ID. Những bộ xáo trộn bít sử dụng trong BICM-ID được giới thiệu trong các tài liệu [4, 8, 10] có hiệu quả cao nhưng thuật toán phức tạp và triển khai phần cứng thực tế khó. Trong bài báo này, chúng tôi nghiên cứu về các bộ xáo trộn cơ bản, từ đó, đề xuất một bộ xáo trộn mới có hiệu suất tốt và dễ triển khai trong thực tế. Phần hai của bài báo trình bày mô hình hệ thống BICM-ID, trong phần ba trình bày khái quát các bộ xáo trộn cơ bản và đề xuất bộ xáo trộn bít mới. Phần bốn và phần năm trình bày kết quả mô phỏng kết luận của bài báo. 2. MÔ HÌNH HỆ THỐNG BICM-ID 2.1. Hệ thống BICM-ID Hình 1. Mô hình hệ thống BICM-ID. Sơ đồ khối của hệ thống BICM-ID thể hiện trong hình 1. Ở phía phát của hệ thống BICM-ID bộ mã xoắn với tỷ lệ /k n thực hiện mã hóa k bit thông tin đầu vào 1 2, ,..., kt u u u u thành n bit mã đầu ra 1 2, ,..., nt c c c c , bộ xáo trộn bit (thường là bộ xáo trộn giả ngẫu nhiên) có chiều dài N thực hiện xáo trộn các bit mã 1 2 1 2 1 2 1 1 1 2 2 2 / / /, ,..., , , ,..., ,....., , ,..., , n n n t N n N n N nc c c c c c c c c c sau đó, các bit được chia thành các Kỹ thuật điều khiển & Điện tử V. T. Thắng, N. V. Giáo, N. T. Quang, “Thiết kế bộ xáo trộn cho qua kênh pha đinh.” 60 nhóm 1 2, ,..., mt t t tv v v v (với 2logm M , 1,2,..., /t N m ) để ánh xạ vào một symbol tx trong bộ tín hiệu bằng một kiểu dán nhãn : 0,1 ,t t tx v x (1) Tín hiệu tx được truyền qua kênh có hệ số pha đinh ta và tạp âm tn với mật độ công suất một phía 0N . Đầu thu hệ thống sử dụng bộ tách sóng tín hiệu nhất quán thu được tín hiệu sau [7]: .t t t ty a x n (2) Trên kênh pha đinh, ta có phân bố Rayleigh với 2 1tE a . Hệ số pha đinh ta được ước lượng đầy đủ khi thông tin trạng thái kênh (CSI-Channel State Information) hoàn hảo. Tại đầu thu của hệ thống bộ giải điều chế dùng tín hiệu nhận được ty và giá trị tỷ lệ hợp lẽ cực đại theo hàm logarit (LLR - Log Likelihood Ratio) tiên nghiệm của các bit mã hóa để tính giá trị LLR ngoại lai cho mỗi bit itv được xáo trộn trong symbol nhận được là [3]: 1 0 1 1 exp log ; ; exp log ; i t i t m j i t t t t t jx j ii e t m j i t t t t t jx j i p y x v x v I v O p y x v x v I (3) Trong đó: 0,1j tv x giá trị bit thứ j ở nhãn tương ứng tx v ; i b là tập con chứa các symbol mà nhãn nhị phân của nó có giá trị 0,1b tại vị trí i . Ở vòng lặp đầu tiên, các bit đã xáo trộn được giả sử có xác suất như nhau, vì vậy, giá trị LLR tiên nghiệm của nó được đặt bằng không ( ; 0itv I ). Bộ giải mã SISO dựa vào giá trị LLR tiên nghiệm của các bit mã ;itc I , giá trị LLR tiên nghiệmcủa các bit thông tin ;itu I và cấu trúc mã xoắn để tính giá trị LLR ngoại lai của các bit mã ;ie tc O và giá trị LLR ngoại lai của các bit thông tin ;itu O . Sau một số vòng lặp xác định, bộ quyết định cứng dựa trên các giá trị LLR cuối cùng của các bit thông tin ;itu O xác định các bit giải mã. Để giảm bớt độ phức tạp của hệ thống, bộ giải mã SISO thường sử dụng thuật toán Max-Log-Map. 2.2. Ảnh hưởng của bộ xáo trộn đến chất lượng của BICM-ID Quá trình xáo trộn bit thực hiện đưa m bit cách xa nhau trong chuỗi dữ liệu gốc về cùng một symbol kênh. Khoảng cách giữa các bit trong cùng symbol gọi là độ trải bit. Với quá trình xáo trộn lý tưởng, m bit mã trong cùng một symbol kênh là độc lập. Do đó, phản hồi từ các phần dữ liệu tốt ít ảnh hưởng của nhiễu kênh có thể làm tăng hiệu quả giải mã cho các phần dữ liệu xấu do tác động mạnh bởi nhiễu. Nói cách khác, các phản hồi (các giá trị LLR ;itv I ) sử dụng trong phương trình 3 để tính toán lại giá trị LLR ngoại lai Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN ... qua kênh pha đinh.” 62 Vì vậy, trong phần sau của bài báo này, chúng tôi đề xuất bộ xáo trộn mới khai thác ưu điểm và khắc phục nhược điểm của kỹ thuật này. a) Viết dữ liệu vào. b) Dữ liệu xáo trộn. c) Dữ liệu giải xáo trộn. Hình 3. Ví dụ dữ liệu xáo trộn chịu tác động lỗi cụm. Trong tài liệu [2, 11] có kỹ xáo trộn tương tự như trên trong quá trình ghi dữ liệu vào, nhưng quá trình đọc ra dữ liệu được đọc theo đường chéo của ma trận ô nhớ. 3.2.2. Xáo trộn giả ngẫu nhiên Kỹ thuật xáo trộn giả ngẫu nhiên sử dụng các hàm đại số thực hiện xáo trộn các số nguyên 1,2,..., N ( N là độ dài khối bit xáo trộn) để tạo ra vector xáo trộn. Trong bài báo này, chúng tôi trình bày ba kỹ thuật xáo trộn điển hình: Relative Prime, Golden Relative Prime và Dithered Relative Prime, trong đó, vector xáo trộn được xác định dựa vào giá trị 5 1 / 2 0,618g (hệ số Golden) [2, 5]. Hình 4 trình bày cụ thể ba nguyên tắc xáo trộn trên đây. Trong đó: m : Là số nguyên bất kỳ khác không (thường chọn 1m hoặc 2m ). r : Là số nguyên bất kỳ khác không xác định khoảng cách giữa các bit đầu vào bất kỳ được trải ra lớn nhất. j : Là số nguyên bất kỳ được lựa chọn trước của phép chia modul cho r (thường 0j ). ( )d n : Thành phần nhiễu loạn thứ n của vector nhiễu loạn d có phân bố D xác định trước. s : Chỉ số bắt đầu là một số nguyên được lựa chọn trước. Trong các kỹ thuật xáo trộn trên, hiệu quả của kỹ thuật xáo trộn Relative Prime phụ thuộc vào việc lựa chọn tham số p . Kỹ thuật xáo trộn Golden Relative Prime và Dithered Relative Prime có chất lượng tốt là do mối quan hệ địa chỉ giữa đầu ra và đầu vào gần giống ngẫu nhiên. Do đó, các bộ xáo trộn thiết kế mới thường được so sánh với chúng. Nhược điểm các bộ xáo trộn sử dụng kỹ thuật giả ngẫu nhiên là sử dụng hàm đại số để xác định vector xáo trộn và phải biết trước độ dài khối xáo trộn, vì vậy, khi cần mở rộng kích thước bộ xáo trộn phải tính lại vector xáo trộn. Kích thước bộ xáo trộn lớn do phải Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 69, 10 - 2020 63 lưu trữ chỉ mục xáo trộn. Quá trình đọc dữ liệu ra phức tạp bởi không có quy luật do mang tính gần như ngẫu nhiên. Như vậy, bộ xáo trộn sử dụng kỹ thuật này thường khó triển khai trong thực tế. a) Relative Prime. b) Golden Relative Prime. c) Dithered Relative Prime. Hình 4. Sơ đồ thuật toán tìm véc tơ xáo trộn. 3.2.3. Xáo trộn ngẫu nhiên a) Xáo trộn ngẫu nhiên Trong kỹ thuật xáo trộn xáo trộn này khi độ dài khối bit là N sẽ có !N vector xáo trộn i với 1,2,..., !i N . Địa chỉ bit đầu ra trong kỹ thuật xáo trộn này được chọn lần lượt một cách ngẫu nhiên từ một trong N bit địa chỉ đầu vào. Có N bước xác định địa chỉ đầu ra: + Bước 1: Chọn một số nguyên ngẫu nhiên 1i trong tập N số nguyên 1,2,..., N có xác suất phân bố đồng dạng 1( ) 1/P i N làm địa chỉ đầu tiên cho véc tơ xáo trộn 1(1) .i + Các bước thứ n tiếp theo ( 1n ): Chọn ni là số nguyên nằm trong tập hợp gồm 1N n số nguyên với 1ni i cũng phân bố đồng dạng và xác suất 1( ) 1/ ( 1)P i N n và đặt địa chỉ thứ n cho véc tơ xáo trộn là ni . + Khi ,n N xác định địa chỉ cuối cùng của bộ xáo trộn. b) Xáo trộn bán ngẫu nhiên (semi-random) Một kỹ thuật ngẫu nhiên khác thường được thực hiện hơn, đó là kỹ thuật bán ngẫu nhiên trong đó các địa chỉ xáo trộn được thiết lập dựa trên điều kiện ràng buộc về khoảng trải S cực tiểu là một số ngẫu nhiên được chọn trước. Để xác định địa chỉ bit đầu ra trong kỹ thuật này gồm các bước cụ thể như sau: + Bước 1: Lựa chọn một số nguyên / 2S N (điều kiện đảm bảo quá trình hội tụ [6]). Kỹ thuật điều khiển & Điện tử V. T. Thắng, N. V. Giáo, N. T. Quang, “Thiết kế bộ xáo trộn cho qua kênh pha đinh.” 64 + Bước 2: Lựa chọn một giá trị 0, 1i N ngẫu nhiên. + Bước 3: So sánh i hiện tại với giá trị prei trước đó. Nếu prei i S loại bỏ i quay lại bước 2; Nếu prei i S chấp nhận i . + Bước 4: Quay trở lại bước 2 cho đến khi tất cả các vị trí N đã được lấp đầy. Kỹ thuật xáo trộn ngẫu nhiên có hiệu quả xáo trộn tốt nhất vì quan hệ địa chỉ giữa dữ liệu đầu vào và đầu ra là ngẫu nhiên. Do đó, kỹ thuật xáo trộn này thường dùng trong mô phỏng hệ thống khi khảo sát hiệu quả thống phụ thuộc vào các yếu tố khác như bộ ánh xạ, mã hóa giải mã. Tuy nhiên, kỹ thuật này không khả thi khi triển khai trong thực tế vì để xác định vector xáo trộn cần tới N bước ngẫu nhiên, cần nhiều bộ nhớ phục vụ cho quá trình ghi nhớ địa chỉ ngẫu nhiên ở mỗi bước. Mạch điện phục vụ quá trình đọc dữ liệu phức tạp nhất so với các kỹ thuật xáo trộn khác vì dữ liệu đọc ra theo quy luật ngẫu nhiên. 3. 3. Thiết kế bộ xáo trộn cho hệ thống BICM-ID qua kênh pha đinh a) Quy tắc bộ xáo trộn mới (New-block) Bộ xáo trộn New-blockbao gồm 1m bộ xáo trộn thành phần như trong hình 2b. Điều này đảm bảo rằng, các bit ở các vị trí khác nhau trên symbol kênh được bảo vệ khác nhau sẽđược phân phối đồng đều dọc theo lưới mắt trong quá trình giải mã. Theo phân tích trong mục 2.2 và công thức (3), thiết kế bộ xáo trộn cần đảm bảo độ trải bit và độ trải phổ lớn để phát huy ưu điểm của quá trình giải mã lặp sử dụng phản hồi mềm. Bộ xáo trộn New-block được thiết kế đạt được những mục tiêu trên. Theo sơ đồ hình 2.b, khối bit mã hóa có chiều dài L chia thành m dòng, tương ứng với 2logm M bit đầu vào của bộ điều chế M -mức. Mỗi dòng có /N L m bit. Quá trình xáo trộn trên từng dòng gồm các bước sau: Bước 1: Tiến hành dịch vòng trên mỗi dòng theo quy tắc sau: - Dòng thứ nhất giữ nguyên. - Dòng 2,3,...,i m dịch sang trái lần lượt tương ứng ( 1)i t vị trí, t thỏa mãn điều kiện * 50t m với độ dài khối bit xáo trộn 2000L theo tài liệu tham khảo [13]. Bước 2: Xáo trộn các dòng 2,3,...,i m cùng quy tắc sau: - Dữ liệu viết vào ma trận con có kích thước /m N m theo hàng. - Hoán vị các hàng của các ma trận con để tăng độ phân tán. Bước 3: Dữ liệu ra của mỗi dòng 2,3,...,i m được đọc từ các ma trận con tương ứng theo cột. b) Ví dụ xây dựng bộ xáo trộn New-block cho bộ điều chế 16-QAM Trước khi xáo trộn, khối bit mã hóa có chiều dài L được chia thành 4 dòng tương ứng với 4 bit của bộ điều chế. Mỗi dòng có / 4N L bit. Bước 1: Dịch vòng trên mỗi dòng - Dòng thứ nhất giữ nguyên. - Dòng 2, 3, 4i dịch sang trái lần lượt tương ứng ( 1)i t vị trí, với khối xáo trộn có chiều dài lựa chọn 2048L bit, vậy, 512N bit lựa chọn 16t đảm bảo * 16*4 64 50t m thỏa mãn điều kiện theo tài liệu [13]. Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 69, 10 - 2020 65 Bước 2: Xáo trộn các dòng 2, 3, 4i cùng quy tắc sau: - Dữ liệu viết vào ma trận con có kích thước 4 / 4N theo hàng. - Hoán đổi vị trí các hàng của các ma trận con theo quy luật 3-1-4-2 (hoán vị theo nguyên tắc các hàng xa nhau được đưa lại gần nhau). Bước 3: Dữ liệu ra của mỗi dòng ( 2, 3, 4i ) được đọc từ các ma trận con tương ứng theo cột. 4. KẾT QUẢ MÔ PHỎNG VÀ PHÂN TÍCH Như phân tích trong mục 2.2 và công thức 3, trong kênh pha đinh chất lượng hệ thống BICM-ID bị ảnh hưởng bởi độ trải bit và độ trải symbol của bộ xáo trộn, hai tham số này thường dùng so sánh chất lượng của các bộ xáo trộn với nhau. Ngoài ra, người ta quan tâm đến cấu trúc phần cứng, thời gian xử lý và tính khả thi khi triển khai thực tế của nó khi thiết kế bộ xáo trộn. Xem xét một bộ xáo trộn xây dựng theo sơ đồ hình 2.b sử dụng cho bộ điều chế M-mức cần 1m bộ xáo trộn con 1 1m . Nếu các bộ xáo trộn con là xáo trộn khối thông thường để tận dụng khả năng xáo trộn ta sử dụng các ma trận xáo trộn kích thước tương ứng là 2 / 2 L m ,.., 2 / L m m và đạt được độ trải symbol tối đa là 1m L m m , độ trải bit tối đa là 1 1 m L m m .Còn đối với bộ xáo trộn New-block độ trải symbol cực đại là 1m L m và độ trải bit cực đại * 1 * 1 L N t m t m m . Trong bảng 1 thể hiện so sánh độ trải bit và độ trải symbol của bộ xáo trộn khối thông thường và bộ xáo trộn New- block 16t sử dụng cho bộ điều chế 16-QAM. Rõ ràng bộ xáo trộn New-block có độ trải bit và symbol là lớn hơn. Độ phức tạp và tính khả thi của bộ xáo trộn được so sánh trong bảng 2. Bảng 1. Độ trải của bộ xáo trộn. Bộ xáo trộn Độ trải bit tối đa Độ trải symbol tối đa Xáo trộn khối thông thường (Block) 3 3 4 L 3 4 4 L Xáo trộn New-block 31 1 32 L 3 4 L Bảng 2. Tính phức tạp của các bộ xáo trộn. Tính phức tạp Bộ xáo trộn giả ngẫu nhiên (kỹ thuật Golden) Bộ xáo trộn New-block Bộ nhớ dữ liệu Có sử dụng Có sử dụng Bộ nhớ địa chỉ Có sử dụng Không sử dụng Tính toán vector xáo trộn Cần thiết Không cần thiết Chúng tôi lần lượt tiến hành mô phỏng hệ thống BICM-ID sử dụng bộ điều chế 8-PSK và 16-QAM để đánh giá hiệu suất của bộ xáo trộn New-block. Hình 5 thể hiện hiệu suất BER của hệ thống BICM-ID sử dụng bộ điều chế 8-PSK khi sử dụng các bộ xáo trộn khác nhau. Từ kết quả mô phỏng cho thấy so với bộ xáo trộn khối thông thường thì bộ xáo trộn New-block có hiệu suất vượt trội. Còn so với bộ xáo trộn giả ngẫu nhiên Golden Relative Kỹ thuật điều khiển & Điện tử V. T. Thắng, N. V. Giáo, N. T. Quang, “Thiết kế bộ xáo trộn cho qua kênh pha đinh.” 66 Prime bộ xáo trộn New-blocktrong vùng thác lỗi có chất lượng tốt hơn tại 5ER 2.8*10B độ lợi khoảng 0.25dB , còn ở vùng sàn lỗi tại 5ER 10B độ thiệt công suất khoảng 0.1dB và tại 6ER 5.75*10B độ thiệt công suất khoảng 0.4dB . Hình 5. Hiệu suất của hệ thống BICM-ID sử dụng bộ điều chế 8-PSK. Ngoài ra, với hệ thống BICM-ID sử dụng bộ điều chế 16-QAM chúng tôi còn thực hiện mô phỏng đánh giá sự ảnh hưởng chiều dài khối bit xáo trộn đến hiệu suất BER của hệ thống thể hiện hình 6. Kết quả cho thấy, trong vùng giá trị BER lớn hơn 510 , hiệu suất BER hệ thống có xu hướng tăng khi độ dài của khối bit dữ liệu lớn hơn 3500 bit. Trong vùng giá trị BER nhỏ hơn 510 , khi độ dài khối bit lớn hơn 3000 bit dẫn tới giá trị BER tăng. Trong quá trình mô phỏng chúng tôi lựa chọn độ dài khối bit xáo trộn là 3072 bit để đạt được hiệu suất cao. Hình 6. Ảnh hưởng của độ dài khối bit xáo trộn đến hiệu suất của hệ thống BICM-ID sử dụng bộ điều chế 16-QAM. Nghiên cứu khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 69, 10 - 2020 67 Hình 7 thể hiện hiệu suất của hệ thống BICM-ID sử dụng bộ điều chế 16-QAM trên kênh pha đinh Rayleigh với phổ Doppler là Jakes, tần số dịch chuyển Doppler cực đại 15 Hz sử dụng các bộ xáo trộn khác nhau. Trong vùng thác lỗi, đường cong BER của hệ thống sử dụng bộ xáo trộn New-block có độ dốc lớn hơn đường cong BER của hệ thống sử dụng bộ xáo trộn Block, và có tổn thất công suất khoảng 0.2dB khi so sánh với hai hệ thống sử dụng bộ xáo trộn giả ngẫu nhiên, như trong hình.7a. Vùng sàn lỗi từ giá trị BER=7*10 -5 trở đi (hình 7.b), hệ thống BICM-ID sử dụng bộ xáo trộn New-block có độ lợi hơn hệ thống sử dụng bộ xáo trộn Block ít nhất 3dB và thiệt công suất khoảng 0.2dB so với hệ thống sử dụng bộ xáo trộn giả ngẫu nhiên. Tuy nhiên, hiệu suất của hai hệ thống sử dụng bộ xáo trộn Golden Relative Prime và New-block là tương đương nhau khi SNR đạt 9.5dB . a) Vùng thác lũ. b) Vùng sàn lỗi. Hình 7. Hiệu suất của hệ thống BICM-ID sử dụng bộ điều chế 16-QAM. 5. KẾT LUẬN Bộ xáo trộn New-block có hiệu quả và tính thực tế cao. Như kết quả mô phỏng, hiệu suất của hệ thống BICM-ID sử dụng bộ xáo trộn New-block cao hơn hệ thống sử dụng bộ xáo trộn Block thường, điều này phù hợp với công thức trong bảng 1. Hiệu suất của bộ xáo trộn New-block tương đương với hiệu quả của bộ xáo trộn giả ngẫu nhiên, khi giá trị SNR đạt 9,5dB, nhưng nó có phần cứng đơn giản hơn như thể hiện trong bảng 2. Hơn nữa, kỹ thuật này khai thác được ưu điểm của xáo trộn khối thông thường là dễ thực hiện trong thực tế và có mở rộng kích thước nếu cần. TÀI LIỆU THAM KHẢO [1]. Nguyễn Văn Giáo, “Nghiên cứu cải thiện chất lượng hệ thống BICM-ID trong thông tin vô tuyến” , (2010). [2]. A.S. Barbulescu and S.S Pietrobon, “Interleaver design for turbo codes”, Electronics Letters, Vol.30, (1994), pp.2107-2108. [3]. S. Benedetto, D. Divsalar, G.Momtorsi, F. Pollara, “A soft-input soft-output APP module for iterative decoding of concatenated codes” IEEE Commun. Lett., Vol.1, Jan 1997, pp.22-24. [4]. S. Crozier, J. Lo dge, P. Guinand, and A. Hunt, “Performance of turbo codes with relative prime and golden interleaving strategies”, Proc. The 6th Int. Mobile Satel lite Conf., Ottawa, Ontario, Canada, (1999), pp. 268-275. Kỹ thuật điều khiển & Điện tử V. T. Thắng, N. V. Giáo, N. T. Quang, “Thiết kế bộ xáo trộn cho qua kênh pha đinh.” 68 [5]. G. Caire, G. Taricco, and E. Biglieri, “Bit-interleaved coded modulation,” IEEE Trans. Inform. Theory, Vol. 44, May 1998, pp. 927–945, [6]. S Dolinar and D. Divsalar, “Weight Distribution for Turbo codes Using Random and Nonrandom Permutations”, JPL Progress report 42-122, August 15, 1995, pp. 56-65. [7]. K. Vasudevan, “Digital Communications and Signal Processing”, Department of Electrical Engineering Indian Institute of Technology Kanpur - 208 016 INDIA version 3.1, July 15, 2017. [8]. Purushottama G B, Dr. B R Sujatha “Turbo code with golden section interleaver” International Research Journal of Engineering and Technology (IRJET),Vol.02, June-2015, pp.1069-1073. [9]. Zehavi, E.: “8-PSK trellis codes for a Rayleigh channel”. IEEE Trans. Commun. Vol. 40, No.5, (1992), pp.873–884. [10]. ZOU Xuelan, LIU Weiyan and FENG Guangzeng “Applying Chaotic Maps to Interleaving Scheme Design in BICM-ID” Chinese Journal of Electronics, Vol.19, No.3, July 2010. [11]. Bobby Raje, Karuna Markam, “Review paper on study of various Interleavers and their significance”International Research Journal of Engineering and Technology, Vol.5, Oct 2018, pp.430-434. [12]. Alex Alvarado, Leszek Szczecinski, Erik Agrell, and Arne Svensson “ On the Design of Interleavers for BICM Transmission” pdf (2010). [13]. Xiaodong Li, Aik Chindapol, Member, IEEE, and James A. Ritcey “Bit-Interleaved Coded Modulation With Iterative Decoding and 8PSK Signaling”, IEEE TRANSACTIONS ON COMMUNICATIONS, Vol.50, No. 8, AUGUST 2002. ABSTRACT DESIGNING AN INTERLEAVER FOR BICM-ID OVER RAYLEIGH FADING CHANNEL A bit interleaver (called New-block) used in the BICM-ID (Bit-Interleaved Coded Modulation with Iterative Decoding) on Rayleigh fading channel is proposed. In the error floor area, it provide the system with the BER (Bit Error Rate) value that is approximately pseudo-random bit interleavers’s BER but it has simplerhardware. Keywords: Bit-interleaved code modulation with Iterative Decoding (BICM-ID); Interleaver; Rayleigh fading channel. Nhận bài ngày 02 tháng 01 năm 2020 Hoàn thiện ngày 08 tháng 6 năm 2020 Chấp nhận đăng ngày 15 tháng 10 năm 2020 Địa chỉ: 1Khoa Điện, Điện tử - Đại học Sư phạm Kỹ thuật Nam Định; 2Khoa Vô tuyến Điện tử - Học viện Kỹ thuật quân sự. * Email: vuthithang1978@gmail.com.

File đính kèm:

thiet_ke_bo_xao_tron_cho_he_thong_bicm_id_truyen_dan_qua_ken.pdf

thiet_ke_bo_xao_tron_cho_he_thong_bicm_id_truyen_dan_qua_ken.pdf